- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄17102 > CDB4384 (Cirrus Logic Inc)BOARD EVAL FOR CS4384 DAC PDF資料下載

參數(shù)資料

| 型號: | CDB4384 |

| 廠商: | Cirrus Logic Inc |

| 文件頁數(shù): | 19/52頁 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR CS4384 DAC |

| 標準包裝: | 1 |

| DAC 的數(shù)量: | 8 |

| 位數(shù): | 24 |

| 采樣率(每秒): | 192k |

| 數(shù)據(jù)接口: | 串行 |

| DAC 型: | 電壓 |

| 工作溫度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | CS4384 |

| 產(chǎn)品目錄頁面: | 757 (CN2011-ZH PDF) |

| 相關(guān)產(chǎn)品: | CS4384-CQZR-ND - IC DAC 8CH 103DB 192KHZ 48-LQFP 598-1062-ND - IC DAC 8CH 103DB 192KHZ 48LQFP |

| 其它名稱: | 598-1525 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

26

DS620F1

CS4384

4.7

ATAPI Specification

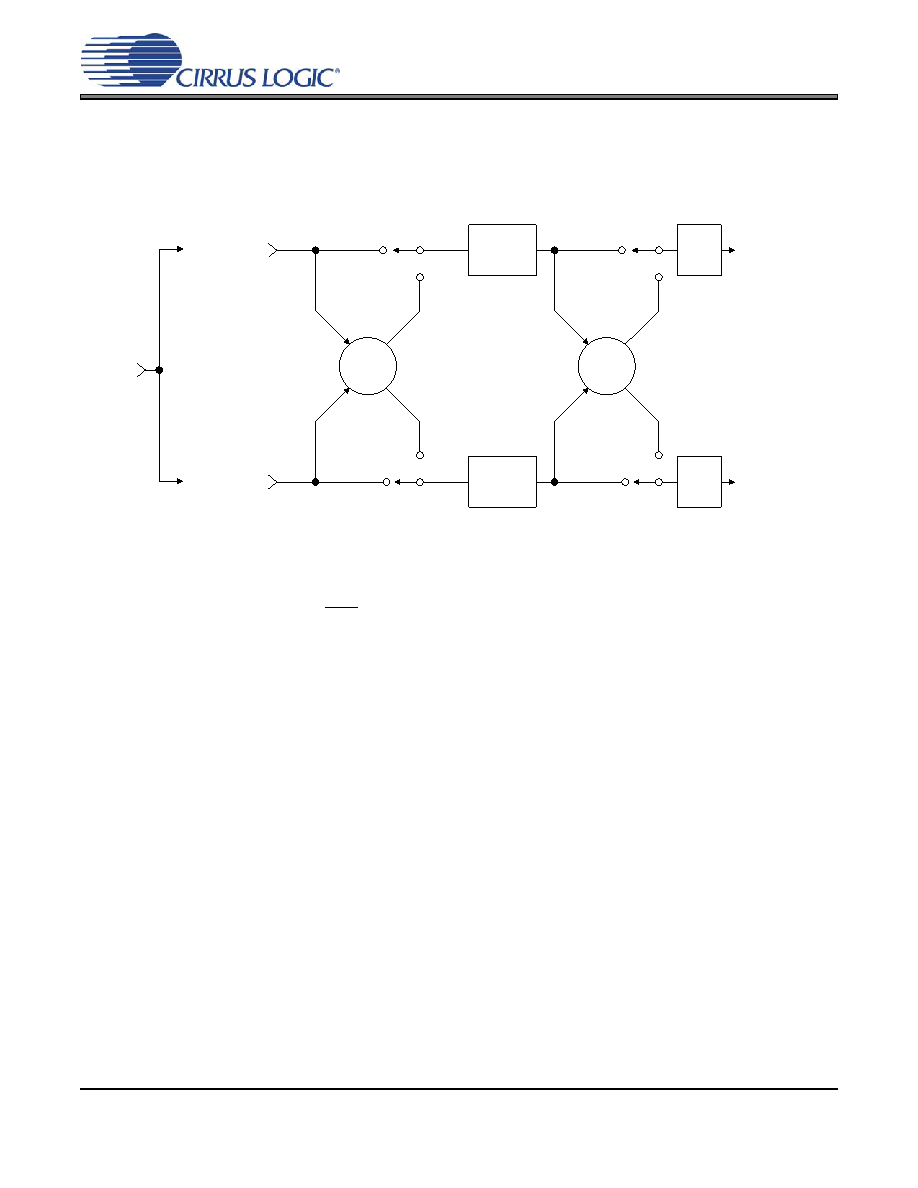

The CS4384 implements the channel mixing functions of the ATAPI CD-ROM specification. The

ATAPI functions are applied per A-B pair. Refer to Table 9 on page 43 and Figure 21 for additional informa-

tion.

4.8

Direct Stream Digital (DSD) Mode

In Software Mode the DSD/PCM bits (Reg. 02h) are used to configure the device for DSD mode. The

DSD_DIF bits (Reg 04h) then control the expected DSD rate and MCLK ratio.

The DIR_DSD bit (Reg 04h) selects between two proprietary methods for DSD to analog conversion. The

first method uses a decimation free DSD processing technique which allows for features such as matched

PCM level output, DSD volume control, and 50kHz on chip filter. The second method sends the DSD data

directly to the on-chip switched-capacitor filter for conversion (without the above mentioned features).

The DSD_PM_EN bit (Reg. 04h) selects Phase Modulation (data plus data inverted) as the style of data

input. In this mode the DSD_PM_Mode bit selects whether a 128Fs or 64x clock is used for phase modu-

lated 64x data (see Figure 22). Use of Phase Modulation Mode may not directly effect the performance of

the CS4384, but may lower the sensitivity to board level routing of the DSD data signals.

The CS4384 can detect errors in the DSD data which does not comply with the SACD specification. The

STATIC_DSD and INVALID_DSD bits (Reg. 04h) allow the CS4384 to alter the incoming invalid DSD data.

Depending on the error, the data may either be attenuated or replaced with a muted DSD signal (the

MUTEC pins would be set according to the DAMUTE bit (Reg. 08h)).

More information for any of these register bits can be found in the “Parameter Definitions” on page 49.

The DSD input structure and analog outputs are designed to handle a nominal 0 dB-SACD (50% modulation

index) at full rated performance. Signals of +3 dB-SACD may be applied for brief periods of time however,

performance at these levels is not guaranteed. If sustained +3 dB-SACD levels are required, the digital vol-

ume control should be set to -3.0 dB. This same volume control register affects PCM output levels. There

is no need to change the volume control setting between PCM and DSD in order to have the 0 dB output

levels match (both 0 dBFS and 0 dB-SACD will output at -3 dB in this case).

ΣΣ

A Channel

Volume

Control

Aout Ax

AoutBx

Left Channel

Audio Data

Right Channel

Audio Data

BChannel

Volume

Control

MUTE

SDINx

Figure 21. ATAPI Block Diagram (x = channel pair 1, 2, 3, or 4)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT-S-26-4/4/W-25-OE-R | MOD CORD SGL-ENDED 4-4 WHITE 25' |

| CDB4398 | BOARD EVAL FOR CS4398 DAC |

| AT-S-26-4/4/S-25-R | MOD CORD STANDARD 4-4 SILVER 25' |

| GBM24DCCS-S189 | CONN EDGECARD 48POS R/A .156 SLD |

| AD9744ACP-PCBZ | BOARD EVAL FOR AD9744ACP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CDB4385 | 功能描述:音頻 IC 開發(fā)工具 Eval Bd 8-Ch DAC w/DSD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| CDB4390 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:24-Bit, Stereo D/A Converter for Digital Audio |

| CDB4391 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:24-Bit, 192 kHz Stereo DAC with Volume Control |

| CDB4391A | 功能描述:音頻 IC 開發(fā)工具 Eval Bd CS4391A RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| CDB4392 | 功能描述:音頻 IC 開發(fā)工具 Eval Bd 114dB 192kHz DAC w/DSD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

發(fā)布緊急采購,3分鐘左右您將得到回復。