- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366549 > Am79C874 (Advanced Micro Devices, Inc.) NetPHY-1LP Low Power 10/100-TX/FX Ethernet Transceiver PDF資料下載

參數(shù)資料

| 型號: | Am79C874 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | NetPHY-1LP Low Power 10/100-TX/FX Ethernet Transceiver |

| 中文描述: | NetPHY - 1LP低功率10/100-TX/FX以太網(wǎng)收發(fā)器 |

| 文件頁數(shù): | 36/60頁 |

| 文件大?。?/td> | 869K |

| 代理商: | AM79C874 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

36

Am79C874

P R E L I M I N A R Y

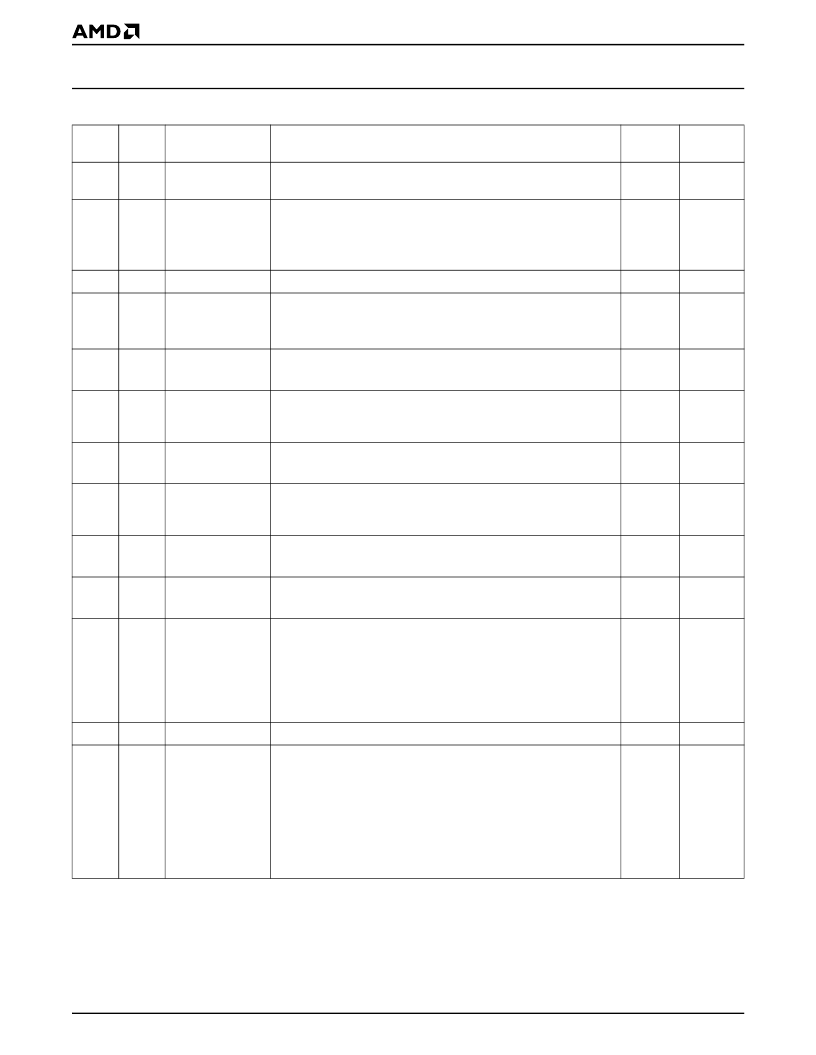

Miscellaneous Features Register (Register 16)

Table 19.

Miscellaneous Features Register (Register 16)

Reg

Bit

Name

Description

Read/

Write

Default

16

15

Repeater

1= Repeater mode, full-duplex is inactive, and CRS only responds

to receive activity. SQE test function is also disabled.

RW

Set by

RPTR

16

14

INTR_LEVL

INTR will be active high if this register bit is set to 1. Pin requires

an external pull-down resistor.

INTR will be active low if this register bit is set to 0. Pin requires

an external pull-up resistor.

RW

0

16

13:12

Reserved

Write as 0, ignore when read.

RW

0

16

11

SQE Test Inhibit

1 = Disable 10BASE-T SQE testing.

0 = Enable 10BASE-T SQE testing. A COL pulse is generated

following the completion of a packet transmission

.

RW

0

16

10

10BASE-T

Loopback

1 = Enable normal loopback in 10BASE-T mode.

0 = Disable normal loopback in 10BASE-T mode.

RW

1

16

9

GPIO_1 Data

When GPIO_1 DIR bit is set to 1, this bit reflects the value of the

GPIO[1] pin. When GPIO_1 DIR bit is set to 0, the value of this bit

will be presented on the GPIO[1] pin.

RW

0

16

8

GPIO_1 DIR

1 = GPIO[1] pin is an input.

0 = GPIO[1] pin is an output.

RW

1

16

7

GPIO_0 Data

When GPIO_0 DIR bit is set to 1, this bit reflects the value of the

GPIO[0] pin. When GPIO[0] DIR bit is set to 0, the value of this bit

will be presented on the GPIO[0] pin.

RW

0

16

6

GPIO_0 DIR

1 = GPIO[0] pin is an input.

0 = GPIO[0] pin is an output.

RW

1

16

5

Auto polarity

Disable

1 = Disable auto polarity detection/correction.

0 = Enable auto polarity detection/correction.

RW

0

16

4

Reverse Polarity

When Register 16.5 is set to 0, this bit will be set to 1 if reverse

polarity is detected on the media. Otherwise, it will be 0.

When Register 16.5 is set to 1, writing a 1 to this bit will reverse

the polarity of the transmitter.

Note: Reverse polarity is detected either through eight inverted

NLPs or through a burst of an inverted FLP.

RW

0

16

3:1

Reserved

Write as 0, ignore when read.

RO

0

16

0

Receive Clock

Control

Writing a 1 to this bit will shut off RX_CLK when incoming data is

not present and only if there is LINK present. RX_CLK will resume

activity one clock cycle prior to RX_DV going high, and shut off 64

clock cycles after RX_DV goes low.

A 0 indicates that RX_CLK runs continuously during LINK

whether data is received or not

In loopback and PCS bypass modes, writing to this bit does not

affect RX_CLK. Receive clock will be constantly active.

RW

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C874VC | NetPHY-1LP Low Power 10/100-TX/FX Ethernet Transceiver |

| AM79C875 | NetPHY⑩ 4LP Low Power Quad 10/100-TX/FX Ethernet Transceiver |

| AM79C875KC | NetPHY⑩ 4LP Low Power Quad 10/100-TX/FX Ethernet Transceiver |

| AM79C875KI | NetPHY⑩ 4LP Low Power Quad 10/100-TX/FX Ethernet Transceiver |

| AM79C901AJC | HomePHY Single-Chip 1/10 Mbps Home Networking PHY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C874KC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Transceiver |

| AM79C874VC | 制造商:Advanced Micro Devices 功能描述:PHY 1-CH 10Mbps/100Mbps 80-Pin TQFP 制造商:AMD (Advanced Micro Devices) 功能描述:PHY 1-CH 10Mbps/100Mbps 80-Pin TQFP |

| AM79C874VD | 制造商:Advanced Micro Devices 功能描述:PHY 1-CH 10Mbps/100Mbps 80-Pin TQFP 制造商:AMD (Advanced Micro Devices) 功能描述:PHY 1-CH 10Mbps/100Mbps 80-Pin TQFP |

| AM79C874VF | 制造商:Advanced Micro Devices 功能描述:PHY 1-CH 10Mbps/100Mbps 80-Pin TQFP 制造商:AMD (Advanced Micro Devices) 功能描述:PHY 1-CH 10Mbps/100Mbps 80-Pin TQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。