- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375269 > ADV7314 (Analog Devices, Inc.) Multiformat 216 MHz Video Encoder with Six NSV 14-Bit DACs PDF資料下載

參數(shù)資料

| 型號: | ADV7314 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Multiformat 216 MHz Video Encoder with Six NSV 14-Bit DACs |

| 中文描述: | 多格式視頻編碼器216兆赫六噪聲整形的14位DAC |

| 文件頁數(shù): | 18/84頁 |

| 文件大小: | 1069K |

| 代理商: | ADV7314 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

REV. 0

–18–

ADV7314

Before writing to the subcarrier frequency registers, the ADV7314

must have been reset at least once since power-up.

The four subcarrier frequency registers must be updated start-

ing with subcarrier frequency register 0 through subcarrier

frequency register 3. The subcarrier frequency will not update

until the last subcarrier frequency register byte has been received

by the ADV7314.

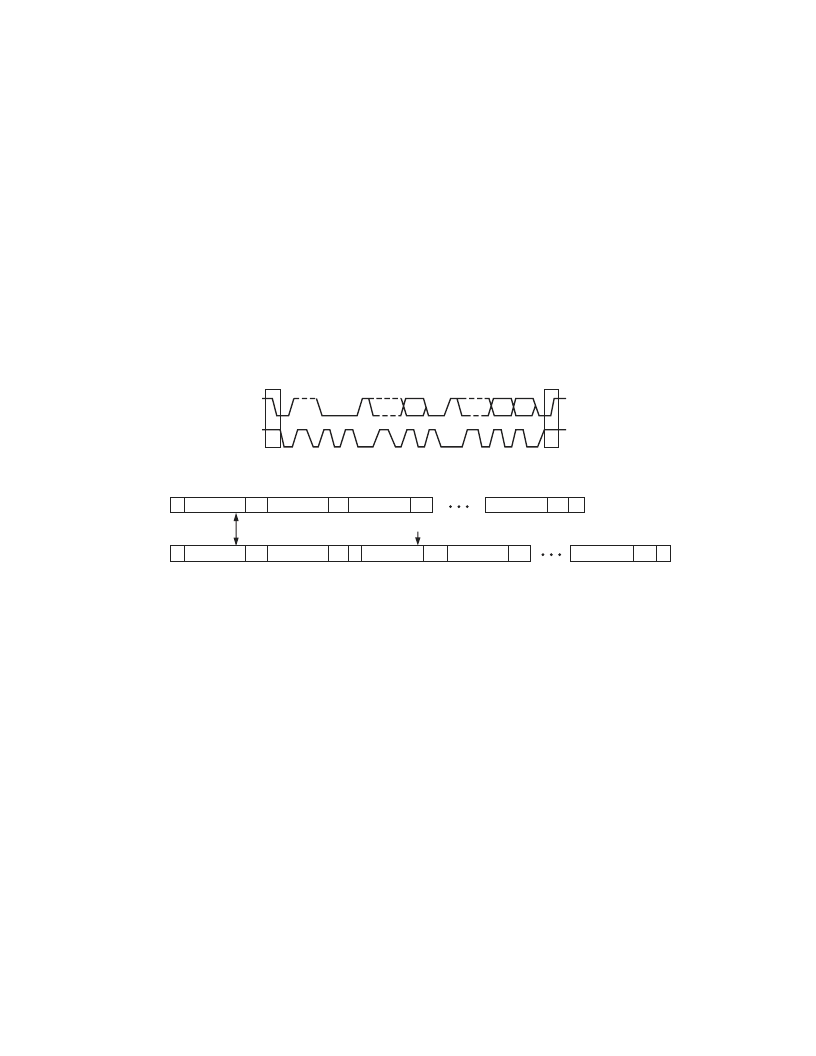

Figure 18 illustrates an example of the data transfer for a write

sequence and the start and stop conditions.

Figure 19 shows bus write and read sequences.

REGISTER ACCESS

The MPU can write to or read from all of the registers of the

ADV7314 except the subaddress registers, which are write-only

registers. The subaddress register determines which register the

SDATA

SCLOCK

START ADRR R/

W

ACK

SUBADDRESS ACK

DATA

ACK

STOP

1–7

8

9

S

1–7

8

9

1–7

8

9

P

Figure 18. Bus Data Transfer

WRITE

SEQUENCE

READ

SEQUENCE

S

SLAVE ADDR

A(S)

SUB ADDR

A(S)

DATA

A(S)

DATA

A(S)

P

S

SLAVE ADDR

A(S)

SUB ADDR

A(S) S

SLAVE ADDR

A(S)

DATA

DATA

A(M)

A

(M)

P

S = START BIT

P = STOP BIT

A(S) = ACKNOWLEDGE BY SLAVE

A(M) = ACKNOWLEDGE BY MASTER

A

(S) = NO-ACKNOWLEDGE BY SLAVE

A

(M) = NO-ACKNOWLEDGE BY MASTER

LSB = 0

LSB = 1

Figure 19. Write and Read Sequence

next read or write operation accesses. All communications with

the part through the bus start with an access to the subaddress

register. A read/write operation is then performed from/to the

target address, which increments to the next address until a stop

command on the bus is performed.

Register Programming

The following section describes the functionality of each register.

All registers can be read from as well as written to unless other-

wise stated.

Subaddress Register (SR7–SR0)

The communications register is an 8-bit write-only register. After

the part has been accessed over the bus and a read/write opera-

tion is selected, the subaddress is set up. The subaddress register

determines to/from which register the operation takes place.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7314KST | Multiformat 216 MHz Video Encoder with Six NSV 14-Bit DACs |

| ADV7322 | Multiformat 11-Bit HDTV Video Encoder |

| ADV7322KSTZ1 | Multiformat 11-Bit HDTV Video Encoder |

| ADV7400 | ADV7402/ADV7400 Multiformat Video Decoders for Advanced TV |

| ADV7400KST-110 | ADV7402/ADV7400 Multiformat Video Decoders for Advanced TV |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7314KST | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat 216 MHz Video Encoder with Six NSV 14-Bit DACs |

| ADV73186702 | 制造商:LG Corporation 功能描述:FRAME ASSEMBLY,DOOR |

| ADV73186703 | 制造商:LG Corporation 功能描述:FRAME ASSEMBLY,DOOR |

| ADV7320 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

| ADV73205705 | 制造商:LG Corporation 功能描述:Frame Assembly |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。