- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374047 > ADV7190KST (ANALOG DEVICES INC) Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs PDF資料下載

參數(shù)資料

| 型號(hào): | ADV7190KST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP64 |

| 封裝: | LQFP-64 |

| 文件頁(yè)數(shù): | 37/69頁(yè) |

| 文件大?。?/td> | 628K |

| 代理商: | ADV7190KST |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)

ADV7190/ADV7191

–37–

REV. 0

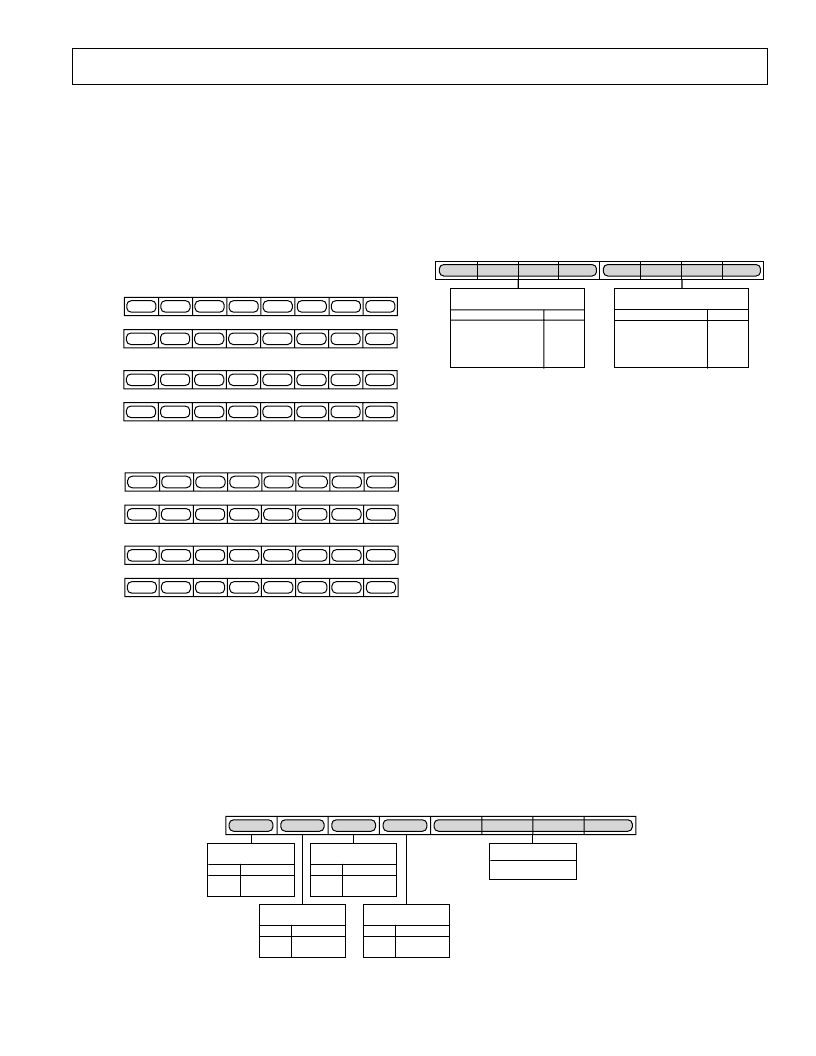

NTSC PEDESTAL/PAL TELETEXT CONTROL

REGISTERS 3–0

(PCE15–0, PCO15–0)/(TXE15–0, TXO15–0)

(Subaddress (SR4–SR0) = 15–18H)

These 8-bit wide registers are used to enable the NTSC pedestal/

PAL Teletext on a line-by-line basis in the vertical blanking

interval for both odd and even

fi

elds. Figures 66 and 67 show

the four control registers. A Logic 1 in any of the bits of these

registers has the effect of turning the Pedestal OFF on the equiva-

lent line when used in NTSC. A Logic 1 in any of the bits of

these registers has the effect of turning Teletext ON on the

equivalent line when used in PAL.

PCO7

PCO6

PCO5

PCO4

PCO3

PCO2

PCO1

PCO0

FIELD 1/3

PCO15

PCO14

PCO13

PCO12

PCO11

PCO10

PCO9

PCO8

FIELD 1/3

PCE15

PCE14

PCE13

PCE12

PCE11

PCE10

PCE9

PCE8

PCE7

PCE6

PCE5

PCE4

PCE3

PCE2

PCE1

PCE0

LINE 17 LINE 16

LINE 15

LINE 14

LINE 13

LINE 12

LINE 11

LINE 10

LINE 25 LINE 24

LINE 23

LINE 22

LINE 21 LINE 20

LINE 19

LINE 18

LINE 17 LINE 16

LINE 15

LINE 14

LINE 13

LINE 12

LINE 11

LINE 10

LINE 25 LINE 24

LINE 23

LINE 22

LINE 21 LINE 20

LINE 19

LINE 18

FIELD 2/4

FIELD 2/4

Figure 66. Pedestal Control Registers

TXO7

TXO6

TXO5

TXO4

TXO3

TXO2

TXO1

TXO0

FIELD 1/3

TXO15

TXO14

TXO13

TXO12

TXO11

TXO10

TXO9

TXO8

FIELD 1/3

TXE15

TXE14

TXE13

TXE12

TXE11

TXE10

TXE9

TXE8

TXE7

TXE6

TXE5

TXE4

TXE3

TXE2

TXE1

TXE0

LINE 14 LINE 13

LINE 12

LINE 11

LINE 10

LINE 9

LINE 8

LINE 7

LINE 22 LINE 21

LINE 20

LINE 19

LINE 18 LINE 17

LINE 16

LINE 15

FIELD 2/4

FIELD 2/4

LINE 14 LINE 13

LINE 12

LINE 11

LINE 10

LINE 9

LINE 8

LINE 7

LINE 22 LINE 21

LINE 20

LINE 19

LINE 18 LINE 17

LINE 16

LINE 15

Figure 67. Teletext Control Registers

TELETEXT REQUEST CONTROL REGISTER (TC07–TC00)

(Address (SR4–SR0) = 1CH)

Teletext Control Register is an 8-bit-wide register. See Figure 68.

TTXREQ Falling Edge Control (TC00–TC03)

These bits control the position of the falling edge of TTXREQ.

It can be programmed from zero clock cycles to a maximum

of 15 clock cycles. This controls the active window for Teletext

data. Increasing this value reduces the amount of Teletext bits

below the default of 360. If Bits TC00

–

TC03 are 00Hex when

Bits TC07

–

TC04 are changed then the falling edge of TTREQ

will track that of the rising edge (i.e., the time between the fall-

ing and rising edge remains constant).

PCLK = clock cycle at 27 MHz.

TTXREQ Rising Edge Control (TC04–TC07)

These bits control the position of the rising edge of TTXREQ.

It can be programmed from zero clock cycles to a maximum of 15

clock cycles.

PCLK = clock cycle at 27 MHz.

TC07

TC06

TC05

TC04

TC03

TC02

TC01

TC00

TC03 TC02 TC01 TC00

0 0 0

0

0 0 1

''

'' '' ''

1

1 1 0

1

1 1 1

0

0 PCLK

1 PCLK

'' PCLK

14 PCLK

15 PCLK

TTXREQ

FALLING EDGE CONTROL

TC07 TC06 TC05 TC04

0 0 0

0

0 0 1

''

'' '' ''

1

1 1 0

1

1 1 1

0

0 PCLK

1 PCLK

'' PCLK

14 PCLK

15 PCLK

TTXREQ

RISING EDGE CONTROL

Figure 68. Teletext Control Register

CGMS_WSS REGISTER 0 C/W0 (C/W07–C/W00)

(Address (SR4–SR0) = 19H)

CGMS_WSS register 0 is an 8-bit-wide register. Figure 69 shows

the operations under control of this register.

C/W0 BIT DESCRIPTION

CGMS Data (C/W00–C/W03)

These four data bits are the

fi

nal four bits of CGMS data out-

put stream. Note it is CGMS data ONLY in these bit positions,

i.e., WSS data does not share this location.

CGMS CRC Check Control (C/W04)

When this bit is enabled (1), the last six bits of the CGMS data,

i.e., the CRC check sequence, is internally calculated by the

ADV7190/ADV7191. If this bit is disabled (0), the CRC values

in the register are output to the CGMS data stream.

CGMS Odd Field Control (C/W05)

When this bit is set (1), CGMS is enabled for odd

fi

elds. Note

this is only valid in NTSC mode.

CGMS Even Field Control (C/W06)

When this bit is set (1), CGMS is enabled for even

fi

elds. Note

this is only valid in NTSC mode.

WSS Control (C/W07)

When this bit is set (1), wide screen signalling is enabled. Note

this is only valid in PAL mode.

C/W07

C/W06

C/W05

C/W04

C/W03

C/W02

C/W01

C/W00

0

1

DISABLE

ENABLE

C/W07

WSS CONTROL

0

1

DISABLE

ENABLE

C/W05

CGMS ODD FIELD

CONTROL

0

1

DISABLE

ENABLE

C/W06

CGMS EVEN FIELD

CONTROL

0

1

DISABLE

ENABLE

C/W04

CGMS CRC CHECK

CONTROL

C/W03

–

C/W00

CGMS DATA

Figure 69. CGMS_WSS Register 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7191 | Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| ADV7191KST | Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| ADV7190 | Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| ADV7192KST | Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs |

| ADV7192 | Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7190KSTZ | 制造商:Analog Devices 功能描述:Video Encoder 6DAC 10-Bit 64-Pin LQFP |

| ADV7191 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| ADV7191KST | 制造商:Analog Devices 功能描述:Video Encoder 6DAC 10-Bit 64-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:54M 4X STD DEF ENCODER NON-MACRO I.C. - Tape and Reel |

| ADV7191KSTZ | 制造商:Analog Devices 功能描述:Video Encoder 6DAC 10-Bit 64-Pin LQFP 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7192 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。