- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374047 > ADV7190KST (ANALOG DEVICES INC) Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs PDF資料下載

參數(shù)資料

| 型號(hào): | ADV7190KST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP64 |

| 封裝: | LQFP-64 |

| 文件頁數(shù): | 33/69頁 |

| 文件大小: | 628K |

| 代理商: | ADV7190KST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

ADV7190/ADV7191

–33–

REV. 0

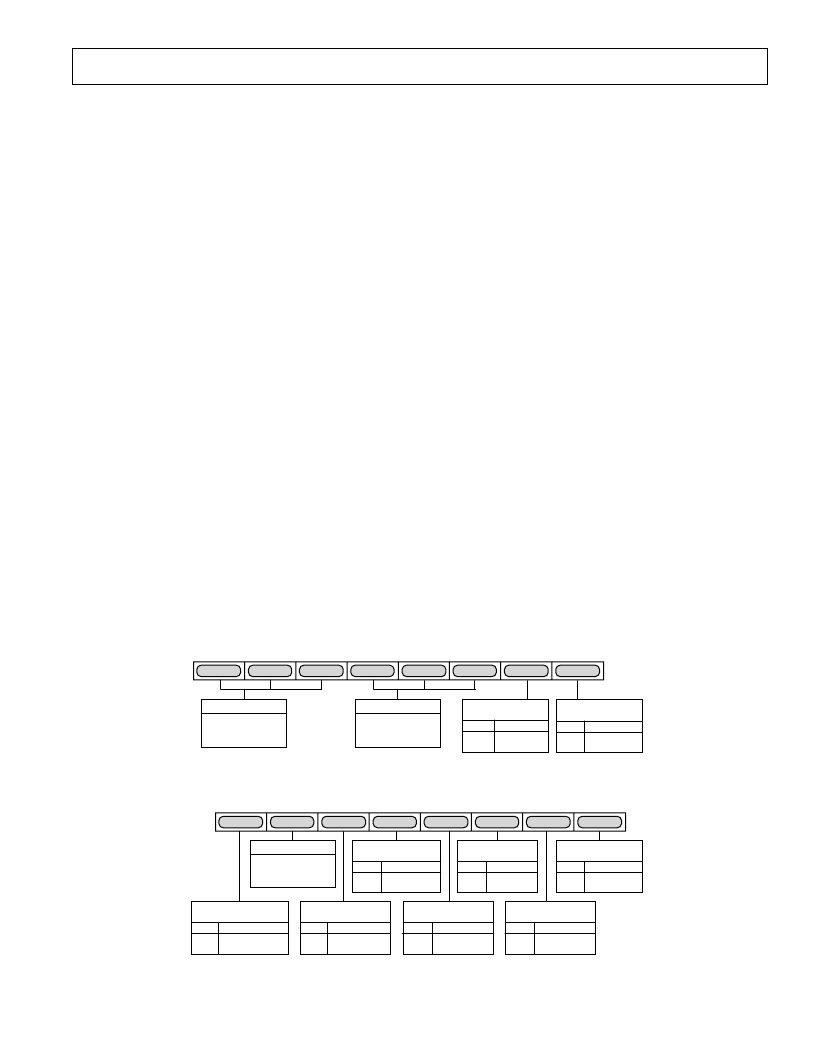

MODE REGISTER 6

MR6 (MR67–MR60)

(ADDRESS (SR4–SR0) = 06H)

Mode Register 6 is an 8-bit-wide register. Figure 56 shows the

various operations under the control of Mode Register 6.

MR6 BIT DESCRIPTION

Power-Up Sleep Mode Control (MR60)

After

RESET

is applied this control is enabled (MR60 = 0) if

both SCRESET/RTC/TR and NTSC_PAL pins are tied high.

The ADV7190/ADV7191 will then power up in Sleep Mode to

facilitate low power consumption while the I

2

C is initialized.

When this control is disabled (MR60 = 1, via the I

2

C) Sleep

Mode control passes to Sleep Mode Control, MR27.

PPL Enable Control (MR61)

The PLL control should be enabled (MR61 = 0 ) when 4

×

Oversampling is enabled (MR16 = 1). It is also used to reset the

PLL when this bit is toggled.

Reserved (MR62, MR63, MR64)

A Logic 0 must be written to these bits.

Field Counter (MR65, MR66, MR67)

These three bits are read-only bits. The field count can be read

back over the I

2

C interface. In NTSC mode the field count goes

from 0–3, in PAL Mode from 0–7.

MODE REGISTER 7

MR7 (MR77–MR70)

(Address (SR4–SR0) = 07H)

Mode Register 7 is an 8-bit wide register. Figure 57 shows the

various operations under the control of Mode Register 7.

MR7 BIT DESCRIPTION

Color Control Enable (MR70)

This bit is used to enable control of contrast and saturation of

color. If this bit is set (1) color controls are enabled (Contrast

Control Register, U-Scale Register, V-Scale Register). If this bit

is set (0), the color control features are disabled.

Luma Saturation Control (MR71)

When this bit is set (1), the luma signal will be clipped if it reaches

a limit that corresponds to an input luma value of 255 (after

scaling by the Contrast Control Register). This prevents the

chrominance component of the composite video signal being

clipped if the amplitude of the luma is too high. When this bit is

set (0), this control is disabled.

Hue Adjust Control (MR72)

This bit is used to enable hue adjustment on the composite and

chroma output signals of the ADV7190/ADV7191. When this

bit is set (1), the hue of the color is adjusted by the phase offset

described in the Hue Adjust Control Register. When this bit is

set (0), hue adjustment is disabled.

Brightness Enable Control (MR73)

This bit is used to enable the brightness control of the ADV7190/

ADV7191. The actual brightness level is programmed in the

Brightness Control Register. This value or “setup” level is added to

the scaled Y data. When this bit is set (1), brightness control

is enabled. When this bit is set (0), brightness control is disabled.

Sharpness Filter Enable (MR74)

This bit is used to enable the sharpness control of the luminance

signal on the ADV7190/ADV7191 (Luma Filter Select has to

be set to Extended, i.e., MR04–MR02 = 100). The various

responses of the filter are determined by the Sharpness Con-

trol Register. When this bit is set (1), the luma response is altered

by the amount described in the Sharpness Control Register.

When this bit is set (0), the sharpness control is disabled. See In-

ternal Filter Response section for luma signal responses.

CSO_HSO

Output Control (MR75)

This bit is used to determine whether

HSO

or

CSO

TTL output

signal is output at the

CSO_HSO

pin. If this bit is set 1, then

the

CSO

TTL signal is output. If this bit is set 0, the

HSO

TTL

signal is output.

MR67

MR66

MR65

MR64

MR63

MR62

MR61

MR60

0

1

ENABLED

DISABLED

MR60

POWER-UP SLEEP

MODE CONTROL

0

1

ENABLED

DISABLED

MR61

PLL ENABLE

CONTROL

ZERO MUST

BE WRITTEN

TO THESE BITS

MR64 MR63 MR62

FIELD COUNTER

MR67 MR66 MR65

Figure 56. Mode Register 6 (MR6)

ZERO MUST

BE WRITTEN

TO THIS BIT

MR76

MR77

MR76

MR75

MR74

MR73

MR72

MR71

MR70

0

1

DISABLE

ENABLE

MR74

SHARPNESS FILTER

ENABLE

0

1

VSO

OUTPUT

CLAMP OUTPUT

MR77

CLAMP/

VSO

SELECT

0

1

DISABLE

ENABLE

MR70

COLOR CONTROL

ENABLE

CSO_HSO

OUTPUT CONTROL

MR75

0

1

HSO

OUT

CSO

OUT

0

1

DISABLE

ENABLE

MR72

HUE ADJUST

CONTROL

0

1

DISABLE

ENABLE

MR73

BRIGHTNESS

ENABLE CONTROL

0

1

DISABLE

ENABLE

MR71

LUMA SATURATION

CONTROL

Figure 57. Mode Register 7 (MR7)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7191 | Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| ADV7191KST | Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| ADV7190 | Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| ADV7192KST | Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs |

| ADV7192 | Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7190KSTZ | 制造商:Analog Devices 功能描述:Video Encoder 6DAC 10-Bit 64-Pin LQFP |

| ADV7191 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Video Encoder with Six 10-Bit DACs and Video Encoder with Six DAC Outputs |

| ADV7191KST | 制造商:Analog Devices 功能描述:Video Encoder 6DAC 10-Bit 64-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:54M 4X STD DEF ENCODER NON-MACRO I.C. - Tape and Reel |

| ADV7191KSTZ | 制造商:Analog Devices 功能描述:Video Encoder 6DAC 10-Bit 64-Pin LQFP 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7192 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。