- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374044 > ADV601 (Analog Devices, Inc.) Low Cost Multiformat Video Codec PDF資料下載

參數(shù)資料

| 型號(hào): | ADV601 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 視頻Codec |

| 英文描述: | Low Cost Multiformat Video Codec |

| 中文描述: | 低成本多格式視頻解碼器 |

| 文件頁數(shù): | 17/52頁 |

| 文件大?。?/td> | 606K |

| 代理商: | ADV601 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADV601

–17–

REV. 0

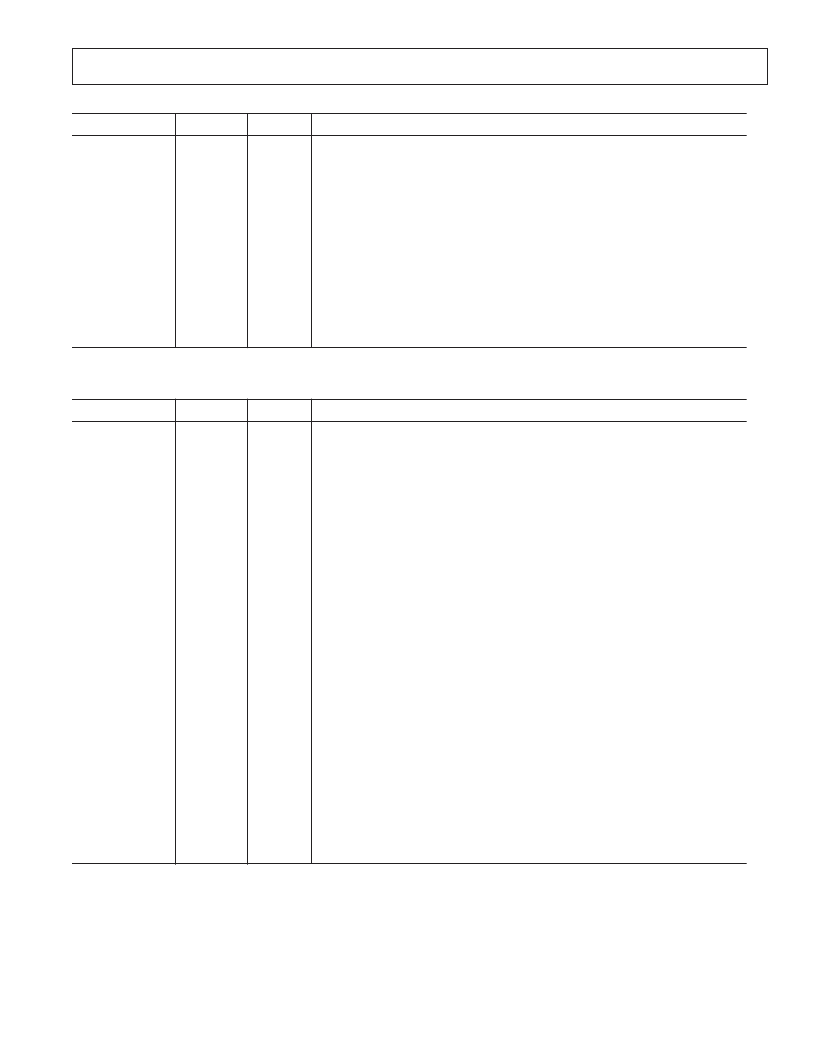

DRAM Interface Pins

Name

Pins

I/O

Description

DDAT[15:0]

16

I/O

DRAM Data Bus. The ADV601 uses these pins for 16-bit data read/write

operations to the external 256K

×

16-bit DRAM. (The operation of the DRAM

interface is fully automatic and controlled by internal functionality of the

ADV601.) These pins are compatible with 30 pF loads.

DRAM Address Bus. The ADV601 uses these pins to form the multiplexed

row/column address lines to the external DRAM. (The operation of the DRAM

interface is fully automatic and controlled by internal functionality of the

ADV601.) These pins are compatible with 30 pF loads.

DRAM Row Address Strobe. This pin is compatible with 30 pF loads.

DRAM Column Address Strobe. This pin is compatible with 30 pF loads.

DRAM Write Enable. This pin is compatible with 30 pF loads.

Note that the ADV601 does not have a DRAM

OE

pin. Tie the DRAM’s

OE

pin to ground.

DADR[8:0]

9

O

RAS

CAS

WE

1

1

1

O

O

O

Serial Port Pins and Timing

DSP Interface Pins

Name

Pins

I/O

Description

TXD

1

O

Serial Transmit Data. Connect this pin to an optional, external DSP’s serial

interface RXData pin. If no DSP is present, this pin may be left unconnected.

This pin is compatible with 30 pF loads.

The TXD pin is for serial data output from the ADV601. Serial data consists of

16-bit words that are transferred most-significant-bit first.

Note that the Mode Control register must be set to indicate whether or not the

external DSP is present.

Serial Receive Data. Connect this pin to an optional, external DSP’s serial

interface TXData pin. If no DSP is present, tie this pin to ground. This pin is

compatible with 30 pF loads.

The RXD pin is for serial data input to the ADV601. Serial data consists of 16-

bit words that are transferred most-significant-bit first.

Note that the Mode Control register must be set to indicate whether or not the

external DSP is present.

Serial Data Clock (VCLK/4). Connect this pin to an optional, external DSP’s

serial interface SCLK pin. If no DSP is present, this pin may be left uncon-

nected. This pin is compatible with 30 pF loads.

The TCLK pin is the serial interface clock. Communication in and out of the

ADV601 requires bits of data to be transmitted after a rising edge of TCLK, and

sampled on a falling edge of TCLK. The DSP must be in external bit clock mode

to use TCLK correctly. The codec drives the TCLK frequency at 1/4 VCLK.

Some typical VCLK and TCLK frequencies are as follows:

VCLK

TCLK (= 1/4 VCLK)

27 MHz

6.75 MHz

29.5 MHz

7.375 MHz

24.54 MHz

6.135 MHz

Note that the Mode Control register must be set to indicate whether or not the

external DSP is present.

RXD

1

I

TCLK

1

O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV601JS | Low Cost Multiformat Video Codec |

| ADV601LC | Ultralow Cost Video Codec |

| ADV601LCJST | Ultralow Cost Video Codec |

| ADV7120KP30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120 | CMOS 80 MHz, Triple 8-Bit Video DAC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV601E-VIDEOPIPE | 制造商:Analog Devices 功能描述:VIDEOPIPE |

| ADV601JS | 制造商:Analog Devices 功能描述:Multiformat Video Codec 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADV601JS12 | 制造商:Analog Devices 功能描述:Multiformat Video Codec 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:DIGITAL VIDEO CODEC REV 1.2 - Bulk |

| ADV601LC | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Cost Video Codec |

| ADV601LCERAG1266B-0.5 | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。