- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1900 > ADSP-21992YBC (Analog Devices Inc)IC DSP CTLR 16BIT 196CSPBGA PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-21992YBC |

| 廠商: | Analog Devices Inc |

| 文件頁(yè)數(shù): | 9/60頁(yè) |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 196CSPBGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | ADSP-21xx |

| 類(lèi)型: | 定點(diǎn) |

| 接口: | SPI,SSP |

| 時(shí)鐘速率: | 150MHz |

| 非易失內(nèi)存: | 外部 |

| 芯片上RAM: | 128kB |

| 電壓 - 輸入/輸出: | 3.30V |

| 電壓 - 核心: | 2.50V |

| 工作溫度: | -40°C ~ 125°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 196-BGA |

| 供應(yīng)商設(shè)備封裝: | 196-MBGA(15x15) |

| 包裝: | 托盤(pán) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

ADSP-21992

Rev. A

|

Page 17 of 60

|

August 2007

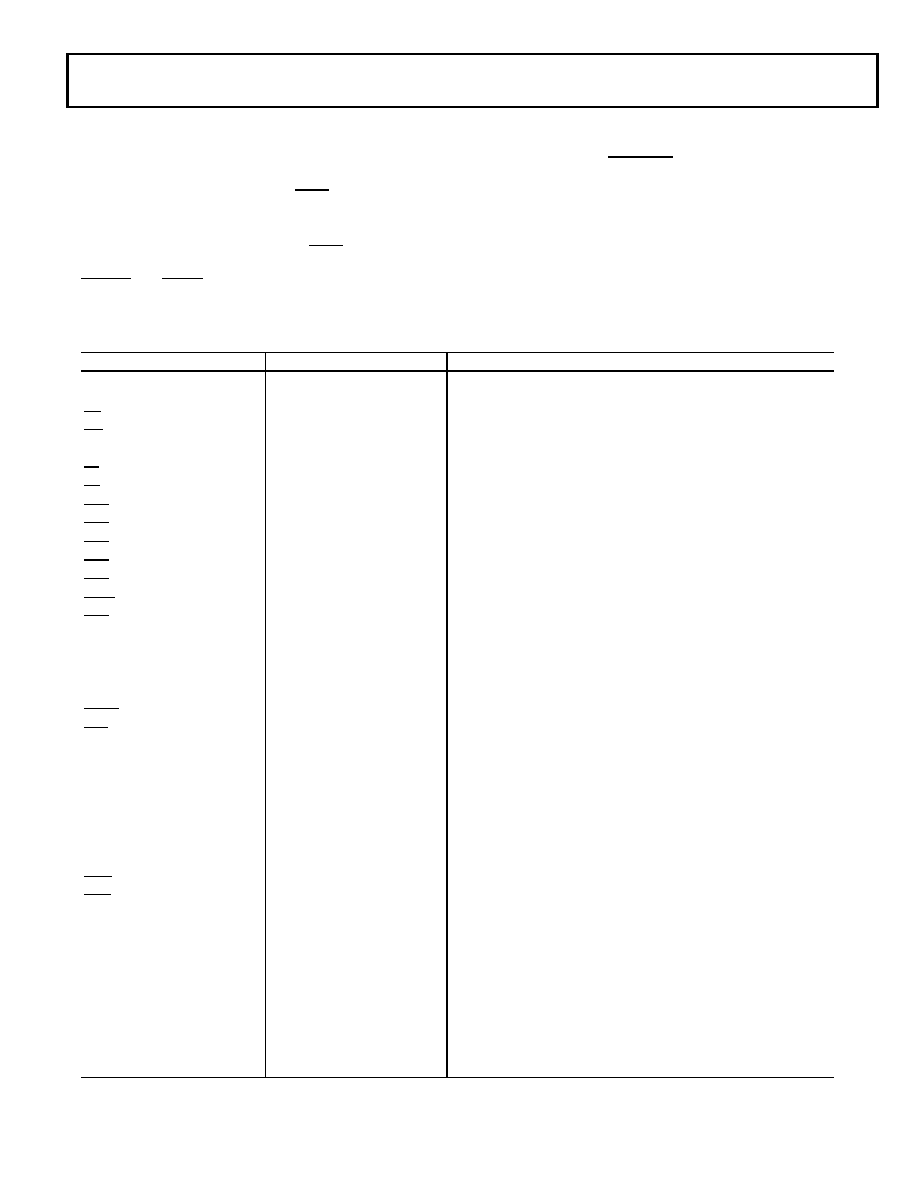

PIN FUNCTION DESCRIPTIONS

ADSP-21992 pin definitions are listed in Table 4. All

ADSP-21992 inputs are asynchronous and can be asserted asyn-

chronously to CLKIN (or to TCK for TRST).

Unused inputs should be tied or pulled to VDDEXT or GND,

except for ADDR21–0, DATA15–0, PF7–0, and inputs that have

internal pull-up or pull-down resistors (TRST, BMODE0,

BMODE1, BMODE2, BYPASS, TCK, TMS, TDI, PWMPOL,

PWMSR, and RESET)—these pins can be left floating. These

pins have a logic level hold circuit that prevents input from

floating internally. PWMTRIP has an internal pull-down, but

should not be left floating to avoid unnecessary PWM

shutdowns.

The following symbols appear in the Type column of Table 4:

G = ground, I = input, O = output, P = power supply,

B = bidirectional, T = three-state, D = digital, A = analog,

CKG = clock generation pin, PU = internal pull-up,

PD = internal pull-down, and OD = open drain.

Table 4. Pin Descriptions

Name

Type

Function

A19–A0

D, OT

External Port Address Bus

D15–D0

D, BT

External Port Data Bus

RD

D, OT

External Port Read Strobe

WR

D, OT

External Port Write Strobe

ACK

D, I

External Port Access Ready Acknowledge

BR

D, I, PU

External Port Bus Request

BG

D, O

External Port Bus Grant

BGH

D, O

External Port Bus Grant Hang

MS0

D, OT

External Port Memory Select Strobe 0

MS1

D, OT

External Port Memory Select Strobe 1

MS2

D, OT

External Port Memory Select Strobe 2

MS3

D, OT

External Port Memory Select Strobe 3

IOMS

D, OT

External Port IO Space Select Strobe

BMS

D, OT

External Port Boot Memory Select Strobe

CLKIN

D, I, CKG

Clock Input/Oscillator Input/Crystal Connection 0

XTAL

D, O, CKG

Oscillator Output/Crystal Connection 1

CLKOUT

D, O

Clock Output (HCLK)

BYPASS

D, I, PU

PLL Bypass Mode Select

RESET

D, I, PU

Processor Reset Input

POR

D, O

Power on Reset Output

BMODE2

D, I, PU

Boot Mode Select Input 2

BMODE1

D, I, PD

Boot Mode Select Input 1

BMODE0

D, I, PU

Boot Mode Select Input 0

TCK

D, I

JTAG Test Clock

TMS

D, I, PU

JTAG Test Mode Select

TDI

D, I, PU

JTAG Test Data Input

TDO

D, OT

JTAG Test Data Output

TRST

D, I, PU

JTAG Test Reset Input

EMU

D, OT, PU

Emulation Status

VIN0

A, I

ADC Input 0

VIN1

A, I

ADC Input 1

VIN2

A, I

ADC Input 2

VIN3

A, I

ADC Input 3

VIN4

A, I

ADC Input 4

VIN5

A, I

ADC Input 5

VIN6

A, I

ADC Input 6

VIN7

A, I

ADC Input 7

ASHAN

A, I

Inverting SHA_A Input

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-3PARCBF548M01 | MODULE BOARD BF548 |

| ADSP-BF506KSWZ-4F | IC DSP 12BIT 400MHZ 120LQFP |

| ADSP-BF518BSWZ-4F4 | IC DSP 16/32B 400MHZ LP 176LQFP |

| ADSP-BF526KBCZ-4C2 | IC DSP CTRLR 400MHZ 289CSPBGA |

| ADSP-BF535PKB-350 | IC DSP CONTROLLER 16BIT 260 BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-21992YST | 制造商:Analog Devices 功能描述: |

| ADSP-21BT101JST | 制造商:Analog Devices 功能描述: |

| ADSP21CSP01BS200 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP21CSP01KS200 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-21MOD810-000 | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。