- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374016 > ADMC330BST (ANALOG DEVICES INC) Single Chip DSP Motor Controller PDF資料下載

參數(shù)資料

| 型號: | ADMC330BST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | Single Chip DSP Motor Controller |

| 中文描述: | 0-BIT, 20 MHz, OTHER DSP, PQFP80 |

| 封裝: | PLASTIC, TQFP-80 |

| 文件頁數(shù): | 15/20頁 |

| 文件大小: | 163K |

| 代理商: | ADMC330BST |

ADMC330

–15–

REV. 0

A software controlled full peripheral reset (including the watch-

dog timer) is achieved by toggling the DSP FL2 flag from 1 to 0

to 1 again.

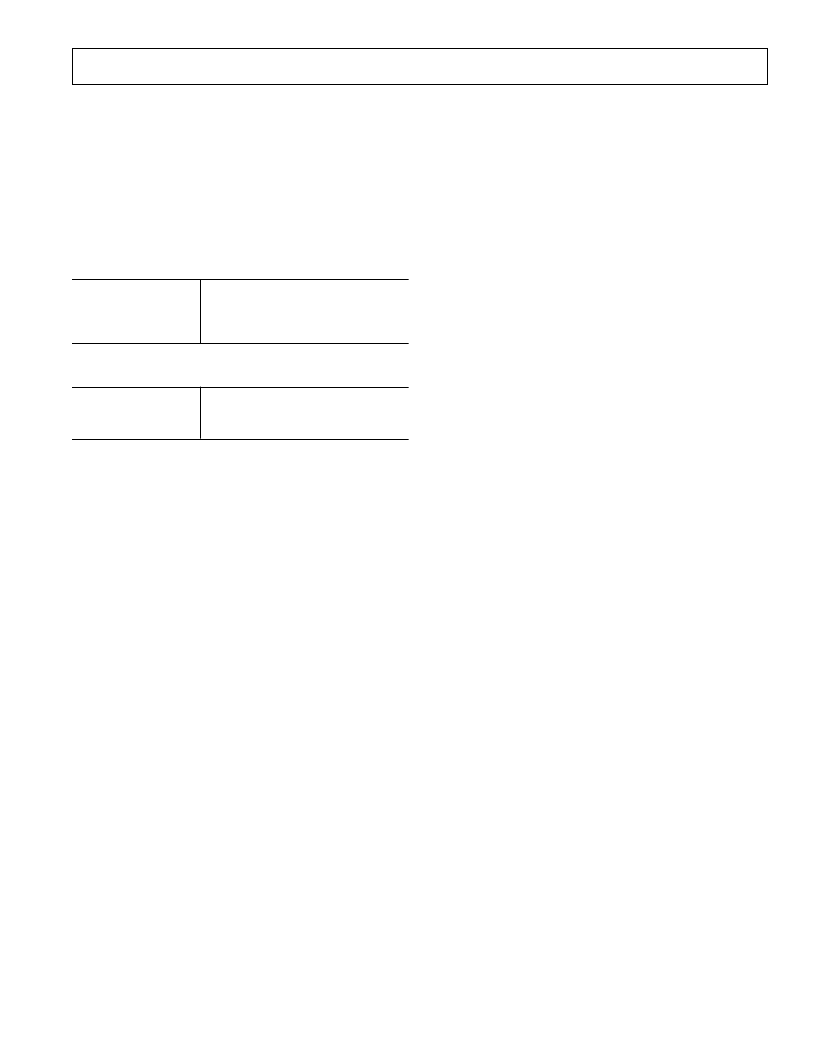

ME MORY MAP

T he ADMC330 has two types of memory: data memory and

program memory. Program RAM starts at 0x0000, while the

program ROM area starts at 0x800. T he data RAM starts at

0x3800 while the peripherals are mapped to a data memory

block starting at 0x2000.

T able V. Program Memory

0x0000–0x002F

0x0030–0x07FF

0x0800–0x0BFF

0x0C00–0x0FFF

Interrupt Vector T able

User Program Space

ROM Monitor

ROM Math Utilities

T able VI. Data Memory

0x2000–0x201F

0x3800–0x3B8F

0x3B90–0x3BFF

Peripherals

User Data Space

Reserved for ROM Monitor Use

ADMC330 Registers

Some registers store values. For example, AX 0 stores an ALU

operand; I4 stores a DAG2 pointer. Other registers consist of

control bits and fields, or status flags. For example, AST AT

contains status flags from arithmetic operations, and fields in

DWAIT control the numbers of wait states for different zones of

data memory.

A secondary set of registers in all computational units allows a

single-cycle context switch.

T he bit and field definitions for control and status registers are

given in the rest of this section, except for IMASK , ICNT L and

IFC, which are defined earlier in this data sheet. T he system

control register, timer registers and SPORT control registers are

all mapped into data memory; that is, registers are accessed by

reading and writing data memory locations rather than register

names. T he particular data memory address is shown with each

memory-mapped register.

Biased Rounding

A new mode allows biased rounding in addition to the normal

unbiased rounding. When the BIASRND bit is set to 0, the

normal unbiased rounding operations occur. When the BIASRND

bit is set to 1, biased rounding occurs instead of the normal unbi-

ased rounding. When operating in biased rounding mode all

rounding operations with MR0 set to 0x8000 will round up,

rather than only rounding odd MR1 values up. For example:

MR value before RND biased RND result

00-0000-8000

00-0001-8000

00-0001-8000

00-0002-8000

00-0000-8001

00-0001-8001

00-0001-8001

00-0002-8001

00-0000-7FFF

00-0000-7FFF

00-0001-7FFF

00-0001-7FFF

unbiased RND result

00-0000-8000

00-0002-8000

00-0001-8001

00-0002-8001

00-0000-7FFF

00-0001-7FFF

T his mode only has an effect when the MR0 register contains

0x8000; all other rounding operation work normally. T his mode

was added to allow more efficient implementation of bit speci-

fied algorithms that specify biased rounding, such as the GSM

speech compression routines. Unbiased rounding is preferred

for most algorithms.

Note: BIASRND bit is Bit 12 of the SPORT 0 Autobuffer

Control register.

INST RUCT ION SE T DE SCRIPT ION

T he ADMC330 assembly language instruction set has an

algebraic syntax that was designed for ease of coding and read-

ability. T he assembly language, which takes full advantage of the

processor’s unique architecture, offers the following benefits:

T he algebraic syntax eliminates the need to remember

cryptic assembler mnemonics. For example, a typical arith-

metic add instruction, such as AR = AX 0 + AY0, resembles a

simple equation.

Every instruction assembles into a single, 24-bit word that can

execute in a single instruction cycle.

T he syntax is a superset ADSP-2100 Family assembly lan-

guage and is completely source and object code compatible

with other family members.

Sixteen condition codes are available. For conditional jump,

call, return or arithmetic instructions, the condition can be

checked and the operation executed in the same instruction

cycle.

Multifunction instructions allow parallel execution of an arith-

metic instruction with up to two fetches or one write to pro-

cessor memory space during a single instruction cycle.

Consult the

ADSP-2100 Family User’s Manual

for a complete

description of the syntax and an instruction set reference with

particular reference to the ADSP-2171 device.

Interrupt E nable

T he ADMC330 supports an interrupt enable instruction. Inter-

rupts are enabled by default at reset. T he instruction source

code is specified as follows:

Syntax:

ENA INT S;

Description:

Executing the ENA INT S instruction allows

all unmasked interrupts to be serviced again.

I

nterrupt Disable

T he ADMC330 supports an interrupt disable instruction. T he

instruction source code is specified as follows:

Syntax:

DIS INT S;

Description:

Reset enables interrupt servicing. Executing

the DIS INT S instruction causes all inter-

rupts to be masked without changing the

contents of the IMASK register. Disabling

interrupts does not affect the autobuffer cir-

cuitry, which will operate normally whether

or not interrupts are enabled. T he disable

interrupt instruction masks all user interrupts

including the power-down interrupt.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADMC401BST | Single-Chip, DSP-Based High Performance Motor Controller |

| ADMC401 | Single-Chip, DSP-Based High Performance Motor Controller |

| ADMC401-ADVEVALKIT | Circular Connector; No. of Contacts:5; Series:MS27497; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:10; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:10-5 RoHS Compliant: No |

| ADMC401-PB | Single-Chip, DSP-Based High Performance Motor Controller |

| ADMCF340 | DashDSPTM 64-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADMC330KP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:AC/DC Motor Controller/Driver |

| ADMC330KP-80 | 制造商:Analog Devices 功能描述: |

| ADMC331 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Single Chip DSP Motor Controller |

| ADMC331-ADVEVALKIT | 制造商:AD 制造商全稱:Analog Devices 功能描述:Single Chip DSP Motor Controller |

| ADMC331BST | 制造商:Analog Devices 功能描述:DSP Motor Controller 80-Pin TQFP 制造商:Analog Devices 功能描述:IC MOTOR CONTROLLER 制造商:Analog Devices 功能描述:SOME BENT LEADS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。