- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36339 > 935267395551 (NXP SEMICONDUCTORS) COLOR SIGNAL DECODER, PBGA156 PDF資料下載

參數(shù)資料

| 型號(hào): | 935267395551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL DECODER, PBGA156 |

| 封裝: | 15 X 15 MM, 1.15 MM HEIGHT, PLASTIC, MS-034, SOT-472-1, BGA-156 |

| 文件頁(yè)數(shù): | 159/178頁(yè) |

| 文件大?。?/td> | 988K |

| 代理商: | 935267395551 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)當(dāng)前第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)

2004 Jul 22

81

Philips Semiconductors

Product specication

Multistandard video decoder with adaptive

comb lter and component video input

SAA7118

10 BOUNDARY SCAN TEST

The SAA7118 has built-in logic and 5 dedicated pins to

support boundary scan testing which allows board testing

without special hardware (nails). The SAA7118 follows the

“IEEE Std. 1149.1 - Standard Test Access Port and

Boundary-Scan Architecture” set by the Joint Test Action

Group (JTAG) chaired by Philips.

The 5 special pins are Test Mode Select (TMS), Test

Clock (TCK), Test Reset (TRST), Test Data Input (TDI)

and Test Data Output (TDO).

The Boundary Scan Test (BST) functions BYPASS,

EXTEST, INTEST, SAMPLE, CLAMP and IDCODE are all

supported; see Table 35. Details about the JTAG

BST-TEST can be found in specification “IEEE Std.

1149.1”. A file containing the detailed Boundary Scan

Description Language (BSDL) description of the SAA7118

is available on request.

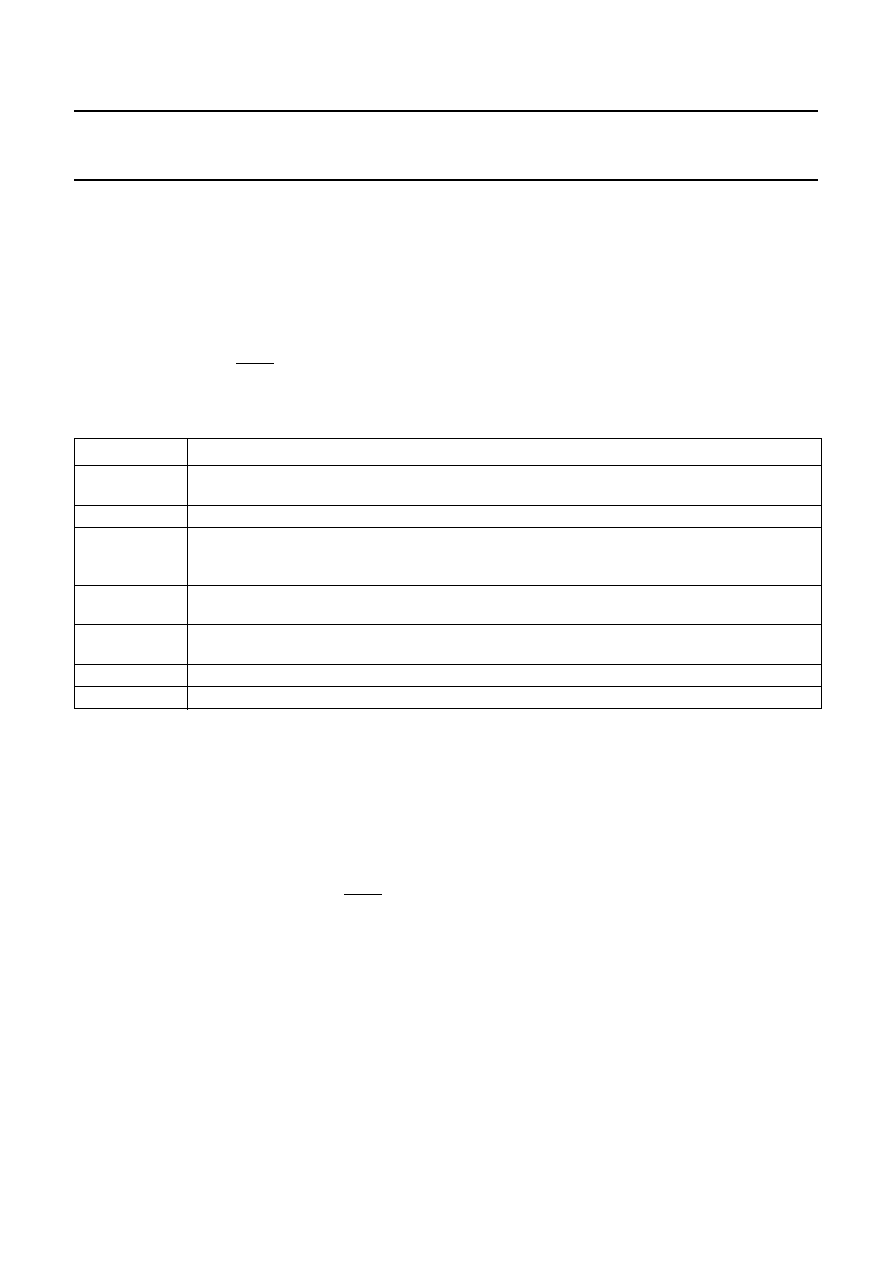

Table 35 BST instructions supported by the SAA7118

INSTRUCTION

DESCRIPTION

BYPASS

This mandatory instruction provides a minimum length serial path (1 bit) between TDI and TDO

when no test operation of the component is required.

EXTEST

This mandatory instruction allows testing of off-chip circuitry and board level interconnections.

SAMPLE

This mandatory instruction can be used to take a sample of the inputs during normal operation of the

component. It can also be used to preload data values into the latched outputs of the boundary scan

register.

CLAMP

This optional instruction is useful for testing when not all ICs have BST. This instruction addresses

the bypass register while the boundary scan register is in external test mode.

IDCODE

This optional instruction will provide information on the components manufacturer, part number and

version number.

INTEST

This optional instruction allows testing of the internal logic (no customer support available).

USER1

This private instruction allows testing by the manufacturer (no customer support available).

10.1

Initialization of boundary scan circuit

The Test Access Port (TAP) controller of an IC should be

in the reset state (TEST_LOGIC_RESET) when the IC is

in functional mode. This reset state also forces the

instruction register into a functional instruction such as

IDCODE or BYPASS.

To solve the power-up reset, the standard specifies that

the TAP controller will be forced asynchronously to the

TEST_LOGIC_RESET state by setting the TRST pin

LOW.

10.2

Device identication codes

A device identification register is specified in “IEEE Std.

1149.1b-1994”. It is a 32-bit register which contains fields

for the specification of the IC manufacturer, the IC part

number and the IC version number. Its biggest advantage

is the possibility to check for the correct ICs mounted after

production and determination of the version number of ICs

during field service.

When the IDCODE instruction is loaded into the BST

instruction register, the identification register will be

connected between pins TDI and TDO of the IC. The

identification register will load a component specific code

during the CAPTURE_DATA_REGISTER state of the TAP

controller and this code can subsequently be shifted out.

At board level this code can be used to verify component

manufacturer, type and version number. The device

identification register contains 32 bits, numbered 31 to 0,

where bit D31 is the most significant bit (nearest to TDI)

and bit D0 is the least significant bit (nearest to TDO);

see Fig.45.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935267395557 | COLOR SIGNAL DECODER, PBGA156 |

| 935268832557 | COLOR SIGNAL DECODER, PQFP160 |

| 935273916518 | COLOR SIGNAL DECODER, PBGA156 |

| 935273916557 | COLOR SIGNAL DECODER, PBGA156 |

| 935268460118 | 1-CHANNEL, SGL POLE SGL THROW SWITCH, PDSO5 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。