- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24809 > 935263011112 (NXP SEMICONDUCTORS) SPECIALTY TELECOM CIRCUIT, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | 935263011112 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PDSO16 |

| 封裝: | PLASTIC, SOT-162, SO-16 |

| 文件頁數(shù): | 30/33頁 |

| 文件大小: | 574K |

| 代理商: | 935263011112 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁

Philips Semiconductors

PCD3316

CIDCW receiver

Product specication

11 March 1999

6 of 30

9397 750 04824

Philips Electronics N.V. 1999. All rights reserved.

Unrestr

icted

The FSK-OVR Error bit (Status register, bit 3) indicates that a previous byte is lost

due to an overrun. The FSK-FRM Error bit (Status register, bit 2) indicates an

incorrect start- or stop-bit. These frame errors indicate that there are synchronization

problems. The on-chip level detector can be used to detect a carrier loss during FSK

transmission. FSK data can be rejected when the signal level is below the reference

level, this to avoid that noise is interpreted as data (Interrupt register, bit 4 is logic 1).

7.4 Ring or polarity change detector

For ring and polarity change detection two comparators are available in the

PCD3316. The reference level of the comparators is set internally by the reference

voltage generator. The voltage levels on the two polarity comparator inputs, POL0

and POL1, are compared with the reference voltage Vref. If POL0 < Vref or

POL1 > Vref, POL0 and POL1 (Status register, bit 7 and 6) are set respectively and

reset if POL0 > Vref and POL1 < Vref. Every time the POL0 status bit changes from

logic 1 to logic 0, a POL0 interrupt is generated. Every time the POL1 status bit

changes from logic 0 to logic 1, a POL1 interrupt is generated.

The period time of a POL1-POL0-POL1 sequence is available in the Ringer period

register. It is preset to 255 on power-on and updated every time a POL1 interrupt is

generated. The sequence is:

1. Power-on: Ringer period register = 255

2. First POL1 interrupt: Ringer period register = 255

3. First POL1 interrupt after a POL0 interrupt: Ringer period register = new time

4. First POL1 interrupt after more than 255

2048 s: Ringer period register = 255.

The period is given in multiples of 1

2048 s. The maximum value is 255.

The POL1-POL0-POL1 sequence is recognized when one or more POL1 interrupts

are generated followed by one or more POL0 interrupts, followed by a POL1 interrupt.

The 32.768 kHz clock is needed for the generation of a polarity interrupt.

7.5 Low battery detection

The low battery voltage detection input (pin LOWBAT) is connected to the positive

input of a comparator. The negative input is connected to the internal reference

voltage. If the voltage on the LOWBAT input pin is less than the reference voltage Vref,

the LOW-BAT Indication (Status register, bit 5) is set. If the LOWBAT input rises

above Vref again, the LOW-BAT Indication is cleared.

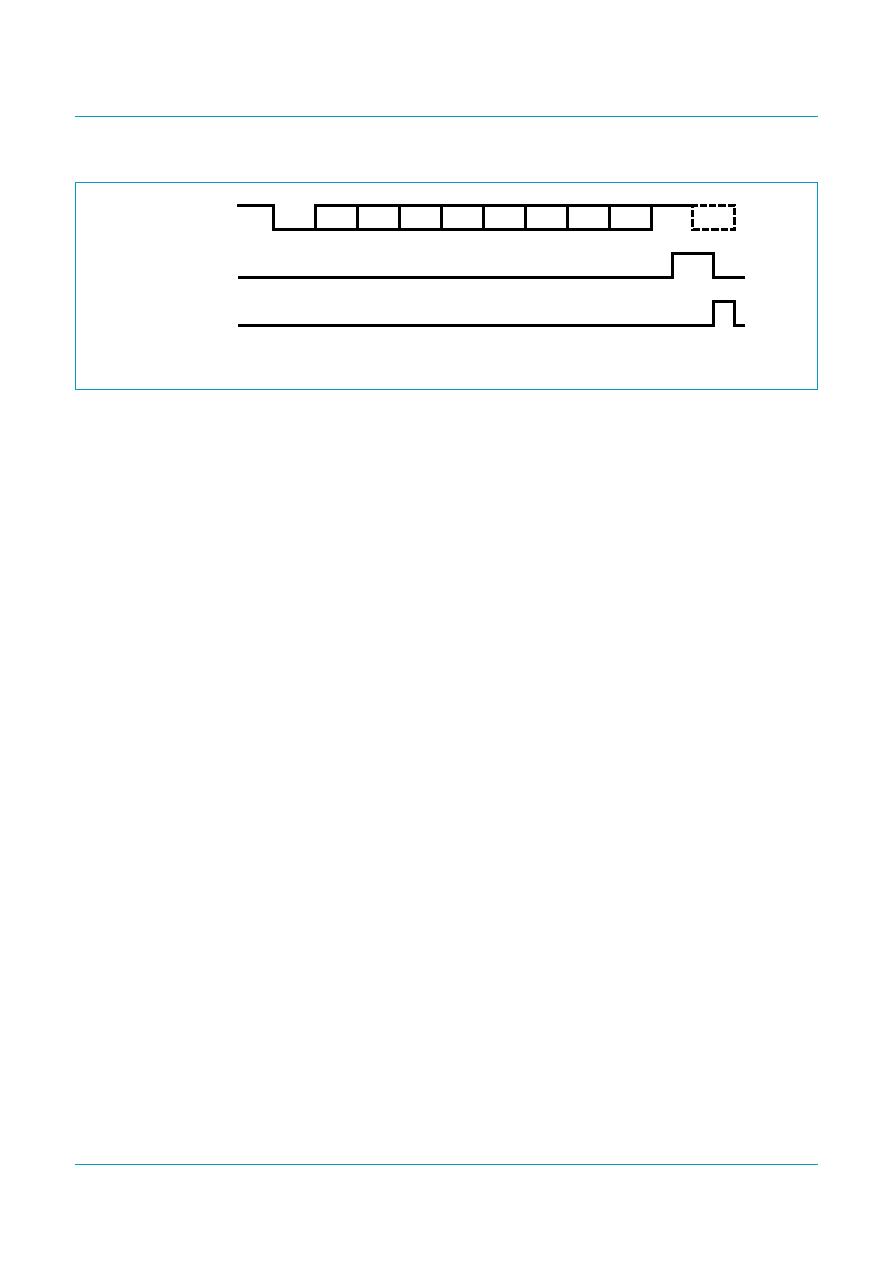

Fig 4.

IRQ generation after reading a valid data byte.

handbook, full pagewidth

MBH981

START

IRQ

read by

serial interface

D0

D1

D2

D3

D4

D5

D6

D7

STOP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935263011118 | SPECIALTY TELECOM CIRCUIT, PDSO16 |

| 935263040118 | AHC SERIES, HEX 1-INPUT INVERT GATE, PDSO14 |

| 935263041112 | AHC SERIES, HEX 1-INPUT INVERT GATE, PDSO14 |

| 935263041118 | AHC SERIES, HEX 1-INPUT INVERT GATE, PDSO14 |

| 935263040112 | AHC SERIES, HEX 1-INPUT INVERT GATE, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。