- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375093 > 7C1351-66 (Cypress Semiconductor Corp.) 128Kx36 Flow-Through SRAM with NoBL TM Architecture PDF資料下載

參數(shù)資料

| 型號: | 7C1351-66 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 128Kx36 Flow-Through SRAM with NoBL TM Architecture |

| 中文描述: | 128K × 36至流通過與總線延遲TM架構(gòu)的SRAM |

| 文件頁數(shù): | 9/13頁 |

| 文件大?。?/td> | 195K |

| 代理商: | 7C1351-66 |

CY7C1351

9

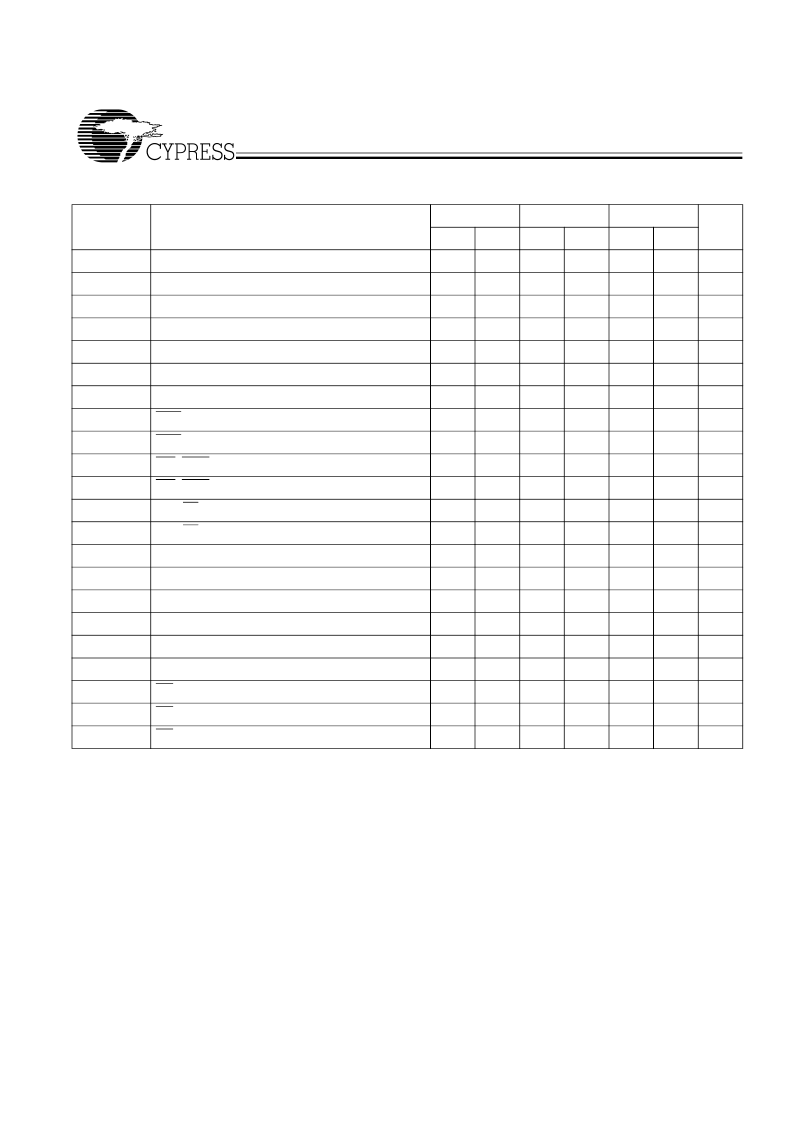

Switching Characteristics

Over the Operating Range

[11, 12, 13]

–

66

–

50

–

40

Parameter

Description

Min.

Max.

Min.

Max.

Min.

Max.

Unit

t

CYC

Clock Cycle Time

15.0

20.0

25.0

ns

t

CH

Clock HIGH

5.0

6.0

7.0

ns

t

CL

Clock LOW

5.0

6.0

7.0

ns

t

AS

Address Set-Up Before CLK Rise

2.0

2.0

2.5

ns

t

AH

Address Hold After CLK Rise

0.5

1.0

1.0

ns

t

CDV

Data Output Valid After CLK Rise

11.0

12.0

14.0

ns

t

DOH

Data Output Hold After CLK Rise

1.5

1.5

1.5

ns

t

CENS

CEN Set-Up Before CLK Rise

2.0

2.0

2.5

ns

t

CENH

CEN Hold After CLK Rise

0.5

1.0

1.0

ns

t

WES

WE, BWS

[3:0]

Set-Up Before CLK Rise

2.0

2.0

2.5

ns

t

WEH

WE, BWS

[3:0]

Hold After CLK Rise

0.5

1.0

1.0

ns

t

ALS

ADV/LD Set-Up Before CLK Rise

2.0

2.0

2.5

ns

t

ALH

ADV/LD Hold after CLK Rise

0.5

1.0

1.0

ns

t

DS

Data Input Set-Up Before CLK Rise

1.7

2.0

2.5

ns

t

DH

Data Input Hold After CLK Rise

0.5

1.0

1.0

ns

t

CES

Chip Select Set-Up

2.0

2.0

2.5

ns

t

CEH

Chip Select Hold After CLK Rise

0.5

1.0

1.0

ns

t

CHZ

Clock to High-Z

[10, 12, 13, 14]

5.0

5.0

5.0

ns

t

CLZ

Clock to Low-Z

[10, 12, 13, 14]

3.0

3.0

3.0

ns

t

EOHZ

OE HIGH to Output High-Z

[10, 12, 13, 14]

6.0

7.0

8.0

ns

t

EOLZ

OE LOW to Output Low-Z

[10, 12, 13, 14]

0

0

0

ns

t

EOV

OE LOW to Output Valid

[12]

6.0

7.0

8.0

ns

Notes:

11. Unless otherwise noted, test conditions assume signal transition time of 2 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output

loading shown in (a) of AC Test Loads.

12. t

, t

CLZ

, t

EOV

, t

EOLZ

, and t

EOHZ

are specified with A/C test conditions shown in part (a) of AC Test Loads. Transition is measured ± 200 mV from steady-state

voltage.

13. At any given voltage and temperature, t

is less than t

and t

is less than t

to eliminate bus contention between SRAMs when sharing the same

data bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worst case user conditions. Device is designed

to achieve High-Z prior to Low-Z under the same system conditions.

14. This parameter is sampled and not 100% tested.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7C1359A-100 | 256K x 18 Synchronous-Pipelined Cache Tag RAM |

| 7C1359A-133 | 256K x 18 Synchronous-Pipelined Cache Tag RAM |

| 7C1359A-150 | 256K x 18 Synchronous-Pipelined Cache Tag RAM |

| 7C1359A-166 | 256K x 18 Synchronous-Pipelined Cache Tag RAM |

| 7C185-12 | 8K x 8 Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 7C1351G-117AZC | 制造商:Cypress Semiconductor 功能描述: |

| 7C1351G-133AZC | 制造商:Cypress Semiconductor 功能描述: |

| 7C1351GC | 制造商:Cypress Semiconductor 功能描述: |

| 7C1351XC | 制造商:Cypress Semiconductor 功能描述: |

| 7C1351XC-RAZC | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。