- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄357464 > 71T016SA20BFGI (INTEGRATED DEVICE TECHNOLOGY INC) 64K X 16 STANDARD SRAM, 20 ns, PBGA48 PDF資料下載

參數(shù)資料

| 型號: | 71T016SA20BFGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 64K X 16 STANDARD SRAM, 20 ns, PBGA48 |

| 封裝: | 7 X 7 MM, PLASTIC, FBGA-48 |

| 文件頁數(shù): | 5/9頁 |

| 文件大?。?/td> | 477K |

| 代理商: | 71T016SA20BFGI |

6.42

5

IDT71T016SA, 2.5V CMOS Static RAM

1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges

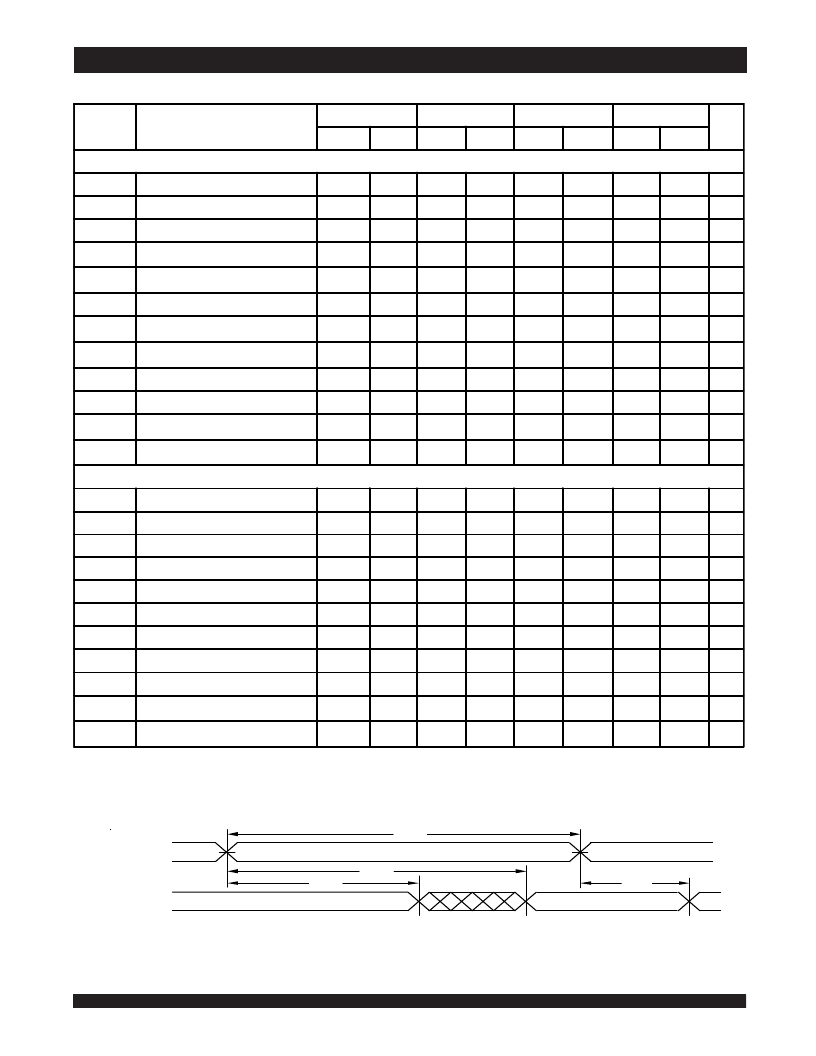

AC Electrical Characteristics

(V

DD

= Mn. to Max., Commercial and Industrial Temperature Ranges)

71T016SA10

(2)

71T016SA12

71T016SA15

71T016SA20

Symbol

Parameter

Min.

Max.

Min.

Max.

Mn.

Max.

Mn.

Max.

Unit

READ CYCLE

t

RC

Read Cycle Time

10

____

12

____

15

____

20

____

ns

t

AA

Address Access Time

____

10

____

12

____

15

____

20

ns

t

ACS

Chip Select Access Time

____

10

____

12

____

15

____

20

ns

t

CLZ

(1)

Chip Select Low to Output in Low-Z

4

____

4

____

5

____

5

____

ns

t

CHZ

(1)

Chip Select High to Output in High-Z

____

5

____

6

____

6

____

8

ns

t

OE

Output Enable Lowto Output Valid

____

5

____

6

____

7

____

8

ns

t

OLZ

(1)

Output Enable Lowto Output in Low-Z

0

____

0

____

0

____

0

____

ns

t

OHZ

(1)

Output Enable High to Output in High-Z

____

5

____

6

____

6

____

8

ns

t

OH

Output Hold fromAddress Change

4

—

4

—

4

—

4

—

ns

t

BE

Byte Enable Lowto Output Valid

—

5

—

6

—

7

____

8

ns

t

BLZ

(1)

Byte Enable Lowto Output in Low-Z

0

____

0

____

0

____

0

____

ns

t

BHZ

(1)

Byte Enable High to Output in High-Z

____

5

____

6

____

6

____

8

ns

WRITE CYCLE

t

WC

Write Cycle Time

10

____

12

____

15

____

20

____

ns

t

AW

Address Valid to End of Write

7

____

8

____

10

____

12

____

ns

t

CW

Chip Select Lowto End of Write

7

____

8

____

10

____

12

____

ns

t

BW

Byte Enable Lowto End of Write

7

____

8

____

10

____

12

____

ns

t

AS

Address Set-up Time

0

____

0

____

0

____

0

____

ns

t

WR

Address Hold fromEnd of Write

0

____

0

____

0

____

0

____

ns

t

WP

Write Pulse Width

7

____

8

____

10

____

12

____

ns

t

DW

Data Valid to End of Write

5

____

6

____

7

____

9

____

ns

t

DH

Data Hold Time

0

____

0

____

0

____

0

____

ns

t

OW

(1)

Write Enable High to Output in Low-Z

3

____

3

____

3

____

3

____

ns

t

WHZ

(1)

Write Enable Lowto Output in High-Z

____

5

____

6

____

6

____

8

ns

5326 tbl 10

Timing Waveform of Read Cycle No. 1

(1,2,3)

NOTES:

1.

WE

is HIGH for Read Cycle.

2. Device is continuously selected,

CS

is LOW.

3.

OE

,

BHE

, and

BLE

are LOW.

NOTES:

1. This parameter is guaranteed with the AC Load (Figure 2) by device characterization, but is not production tested.

2. 0

0

C to +70

0

C temperature range only.

DATA

OUT

ADDRESS

5326 drw 06

t

RC

t

AA

t

OH

t

OH

DATA

OUT

VALID

PREVIOUS DATA

OUT

VALID

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71V416S10PHGI | 256K X 16 STANDARD SRAM, 10 ns, PDSO44 |

| 71V416S12YG | 256K X 16 STANDARD SRAM, 12 ns, PDSO44 |

| 71V416YL12PHG2 | 256K X 16 STANDARD SRAM, 12 ns, PDSO44 |

| 71V424VL15YGI | 512K X 8 STANDARD SRAM, 15 ns, PDSO36 |

| 72.000.0653.0 | 6-6 CONTACT(S), FEMALE-FEMALE, RECTANGULAR ADAPTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71-T6-2-L-1 | 制造商:Birtcher Products 功能描述: |

| 71T6-2-L-A | 制造商:Birtcher Products 功能描述: |

| 71T6-2-L-BL | 制造商:Birtcher Products 功能描述: |

| 71-T6-2-R-4 | 制造商:Birtcher Products 功能描述: |

| 71T6-2-R-A | 制造商:Birtcher Products 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。