- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382753 > Z9974CA DIODE TVS 16V 500W BI-DIR PDF資料下載

參數(shù)資料

| 型號(hào): | Z9974CA |

| 英文描述: | DIODE TVS 16V 500W BI-DIR |

| 中文描述: | 共14名分布式輸出時(shí)鐘驅(qū)動(dòng)器| TQFP封裝| 52PIN |塑料 |

| 文件頁(yè)數(shù): | 3/9頁(yè) |

| 文件大小: | 62K |

| 代理商: | Z9974CA |

3.3V, 125MHz, Multi-Output Zero Delay Buffer

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07090 Rev. *A

06/18/2001

Page 3 of 9

Z9974

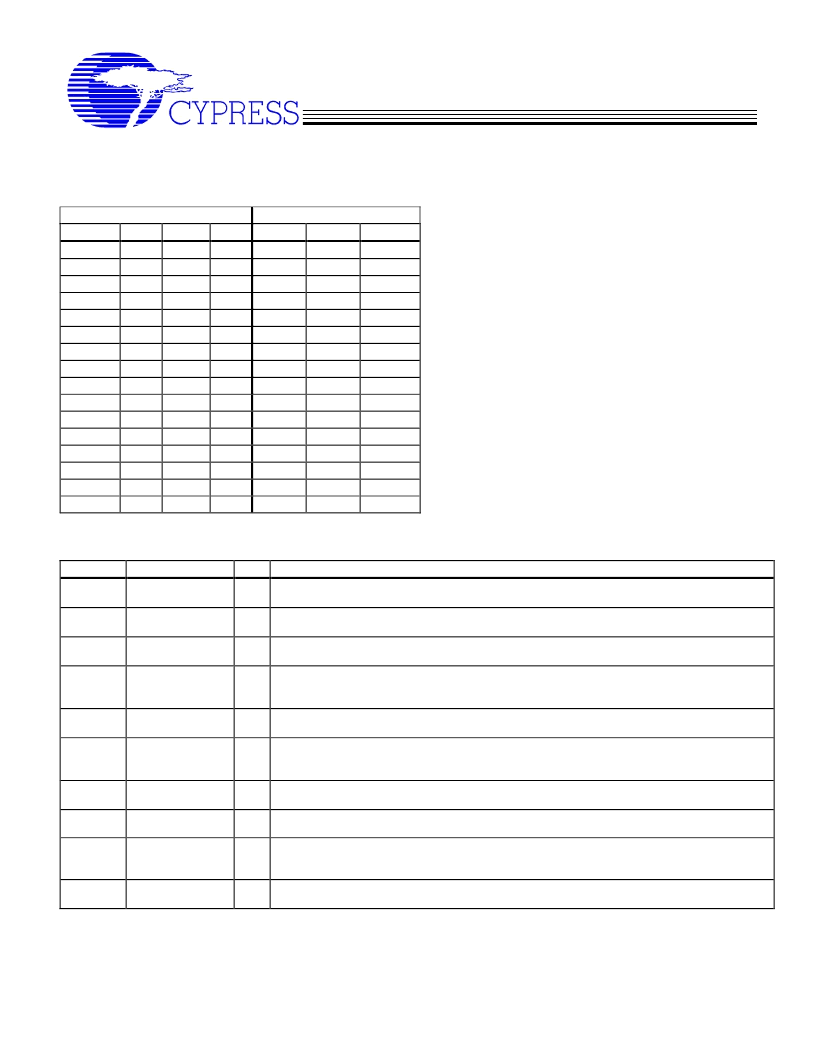

Output Frequency Selection Table

Inputs

VCO_sel

fsela

fselb

0

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

0

1

1

1

0

0

1

0

0

1

0

1

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

Outputs

Qb(0:4)

VCO/4

VCO/4

VCO/8

VCO/8

VCO/4

VCO/4

VCO/8

VCO/8

VCO/8

VCO/8

VCO/16

VCO/16

VCO/8

VCO/8

VCO/16

VCO/16

fselc

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Qa(0:4)

VCO/4

VCO/4

VCO/4

VCO/4

VCO/8

VCO/8

VCO/8

VCO/8

VCO/8

VCO/8

VCO/8

VCO/8

VCO/16

VCO/16

VCO/16

VCO/16

Qc(0:3)

VCO/8

VCO/12

VCO/8

VCO/12

VCO/8

VCO/12

VCO/8

VCO/12

VCO/16

VCO/24

VCO/16

VCO/24

VCO/16

VCO/24

VCO/16

VCO/24

Table 2

PIN DESCRIPTION

PIN No.

2

Pin Name

MR#

I/O

I

Description

Active low Master Reset pin. It has a 250K

internal pull-up. When forced low, all outputs

are Tri-stated (high impedance) and internal ratio dividers are reset.

Active high Output Enable pin. It has a 250K

internal pull-up. When forced low, Qa(0:4),

Qb(0:4), and Qc(0:3) outputs are stopped in a low state. QFB is not effected by this signal.

Input select pins for setting the output dividers at Qa(0:4), Qb(0:4), and Qc(0:3)

respectively. Each pin has an internal 250K

pull-down. See table 2, page 3.

Input pin for bypassing the PLL. It has an internal 250K

pull-up. When forced low,

the input reference clock (applied at TCLK0, or TCLK1) bypasses the PLL and drives the

dividers, typically for device testing. In this case, the PLL is disabled.

Input pin for selecting TCLK0 or TCLK1 as input reference. When TCLK_sel = 0, TCLK0 is

selected, when TCLK_sel = 1, TCLK1 is selected. This pin has a 250K

internal pull-down.

Input pins for applying a reference clock to the PLL. The active input is selected by

TCLK_sel, pin# 8. TCLK0 has a 250K

internal pull-down. TCLK1 has a 250K

internal

pull-up.

Input select pins for setting the Feedback divide ratio at QFB output, pin#29. See table 1,

page1. Each of these pins has a 250K

internal pull-down.

High drive, Low Voltage CMOS, Output clock buffers, Bank Qa. Their divide ratio is

programmed by fsela, pin#7.

Low Voltage CMOS output feedback clock to the internal PLL. The divide ratio for this

output is set by fselFB(0:1). A delay capacitor, or trace may be applied to this pin in order

to control the Input Reference/Output Banks phase relationship.

Feedback input pin. Typically connects to the QFB output for accessing the Feedback to

the PLL. It has a 250K

internal pull-up.

3

OE

I

7,4, 5

Fsel(a,b,c)

I

6

PLL_EN

I

8

TCLK_sel

I

9,10

TCLK(0:1)

I

14, 20

FselFB(0:1)

I

25,23,21,

18,16

29

Qa(0:4)

O

QFB

O

31

FB_In

I

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZAD1025 | DIODE TVS 5.0V 500W UNI-DIR |

| ZAD1030 | Converter IC |

| ZAD1202 | SCR Thyristor; Thyristor Type:Standard Gate; Peak Repetitive Off-State Voltage, Vdrm:1000V; On-State RMS Current, IT(rms):8A; Peak Non Repetitive Surge Current, Itsm:100A; Gate Trigger Current Max, Igt:15uA RoHS Compliant: Yes |

| ZAD2736-2BU | DIODE TVS 180V 400W BIDIR 5% SMA |

| ZAD2744 | Converter IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z9975 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V, 150MHz, Multi-Output Zero Delay Buffer |

| Z9975CA | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V, 150MHz, Multi-Output Zero Delay Buffer |

| Z99SC61235 | 制造商:MINI CIRCU 功能描述:NEW |

| ZA000260R | 制造商:Denon Electronics 功能描述:DENON AM ANTENNA 116010001004S |

| ZA00106FSC | 制造商:Zilog Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。