- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382753 > Z9953AA SCR Thyristor; SCR Type:Standard Gate; Peak Repetitive Off-State Voltage, Vdrm:800V; On-State RMS Current, IT(rms):20A; Peak Non Repetitive Surge Current, Itsm:300A; Gate Trigger Current Max, Igt:30uA PDF資料下載

參數(shù)資料

| 型號(hào): | Z9953AA |

| 英文描述: | SCR Thyristor; SCR Type:Standard Gate; Peak Repetitive Off-State Voltage, Vdrm:800V; On-State RMS Current, IT(rms):20A; Peak Non Repetitive Surge Current, Itsm:300A; Gate Trigger Current Max, Igt:30uA |

| 中文描述: | 八分布式輸出時(shí)鐘驅(qū)動(dòng)器| TQFP封裝| 32腳|塑料 |

| 文件頁數(shù): | 4/6頁 |

| 文件大小: | 43K |

| 代理商: | Z9953AA |

3.3V, 180MHz, Multi-Output Zero Delay Buffer

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07086 Rev. *A

06/18/2001

Page 4 of 6

Z9953

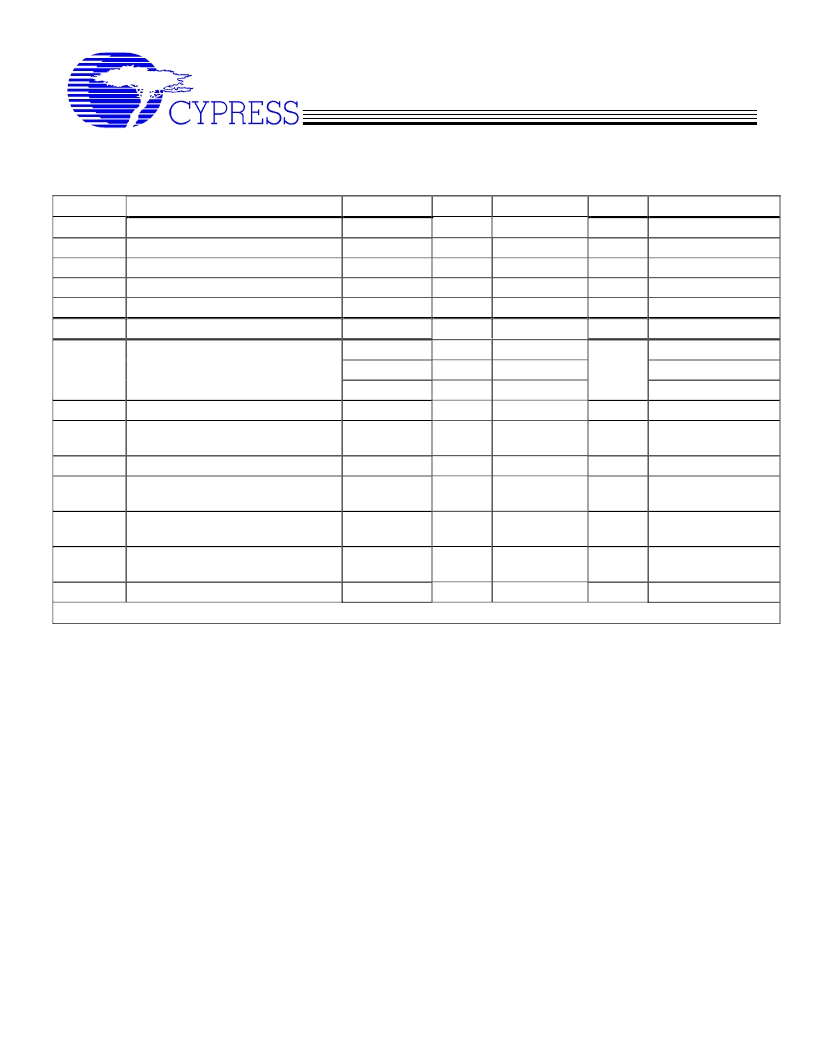

AC Parameters

1

SYMBOL

Tr / Tf

Fref

FrefDC

Fvco

Tlock

Tr / Tf

Fout

PARAMETER

TCLK Input Rise / Fall

Reference Input Frequency

2

Reference Input Duty Cycle

PLL VCO Lock Range

Maximum PLL lock Time

Output Clocks Rise / Fall Time

4,5

Maximum Output Frequency

MIN

TYP

MAX

3.0

110

75

500

10

1.0

110

62.5

200

55

100

UNITS

ns

MHz

%

MHz

ms

ns

MHz

CONDITIONS

25

25

200

0.10

50

25

0.8V to 2.0V

VCO_SEL = ‘0’

VCO_SEL = ‘1’

Bypass Mode

FoutDC

TCCJ

Output Duty Cycle

4,5

Cycle to Cycle Jitter (peak to

peak)

4,5

Any Output to Any Output Skew

4,5

Input to FB_IN Delay (PLL

locked)

3,4,5

Output enable time (all outputs)

45

50

%

ps

TSKEW

Tpd

-

-

-

250

125

ps

ps

-75

tpZL,

tpZH

tpLZ,

tpHZ

Tpd

6

ns

Output disable time (all outputs)

7

ns

Input to Q Delay (PLL bypassed)

3

7

ns

VDD = VDDC = 3.3V +/- 5%, TA = -40

°

C to +85

°

C

Note 1:

Parameters are guaranteed by design and characterization. Not 100% tested in production.

Note 2:

Maximum and minimum input reference is limited by the VCO lock range.

Note 3:

The Tpd (PLL locked) is input reference frequency dependent.

Note 4:

Driving series or parallel terminator 50

(or 50

to VDD/2) transmission lines.

Note 5:

Outputs loaded with 30pF each

Description

The Z9953 is a PLL based clock generator that provides low skew and low jitter clock outputs for high performance

systems. The Z9953 features a differential PLL to minimize cycle-to-cycle and phase jitter. The PLL is

ensured stable operation given that the VCO is configured to run between 200MHz and 500MHz.

The input reference is a differential LVPECL clock. All other control inputs are LVCMOS/LVTTL compatible

The Z9953 features 9 LVCMOS/LVTTL compatible outputs each capable of driving two series terminated 50

transmission lines. With this capability the Z9953 has an effective fan-out of 1:18. The outputs can also be tri-stated when

MR/OE# is set high.

When used as a zero-delay buffer any of the 9 outputs can be used as the feedback input to the PLL. The PLL works to

align the output edge with the input reference edge thus producing a near zero delay.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z9973BA | DIODE TVS 15V 500W UNI-DIR |

| Z9974CA | DIODE TVS 16V 500W BI-DIR |

| ZAD1025 | DIODE TVS 5.0V 500W UNI-DIR |

| ZAD1030 | Converter IC |

| ZAD1202 | SCR Thyristor; Thyristor Type:Standard Gate; Peak Repetitive Off-State Voltage, Vdrm:1000V; On-State RMS Current, IT(rms):8A; Peak Non Repetitive Surge Current, Itsm:100A; Gate Trigger Current Max, Igt:15uA RoHS Compliant: Yes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z9960 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:2.5V/3.3V, 200 MHz Multi-Output Zero Delay Buffer |

| Z9960AL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TWENTY-ONE DISTRIBUTED-OUTPUT CLOCK DRIVER|QFP|48PIN|PLASTIC |

| Z9972 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V, 125-MHz, Multi-Output Zero Delay Buffer |

| Z9972AI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MISCELLANEOUS CLOCK GENERATOR|QFP|52PIN|PLASTIC |

| Z9973 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V, 125-MHz, Multi-Output Zero Delay Buffer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。