- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372950 > XRT73L03IV (EXAR CORP) 3 CHANNEL E3/DS3/STS-1 LINE INTERFCE UNIT PDF資料下載

參數(shù)資料

| 型號: | XRT73L03IV |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 3 CHANNEL E3/DS3/STS-1 LINE INTERFCE UNIT |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PQFP120 |

| 封裝: | 14 X 20 MM, HEAT SINK, TQFP-120 |

| 文件頁數(shù): | 11/53頁 |

| 文件大?。?/td> | 604K |

| 代理商: | XRT73L03IV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

á

XRT73L00

E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.2.0

8

30

LCV/(RCLK2)

O

Line Code Violation Indicator/Receive Clock Output pin 2:

The function of this pin depends upon whether the XRT73L00 is operating in the

HOST Mode, the Hardware Mode or User selection.

HOST Mode - Line Code Violation Indicator Output:

If the XRT73L00 is configured to operate in the HOST Mode, then this pin func-

tions as the LCV output pin by default. However, by using the on-chip Command

Registers, this pin can be configured to function as the second Receive Clock

signal output pin RCLK2.

Hardware Mode - Receive Clock Output pin 2:

This output pin is the Recovered Clock signal from the incoming line signal. The

receive section of the XRT73L00 outputs data via the RPOS and RNEG output

pins on the rising edge of this clock signal.

N

OTE

:

If the XRT73L00 is operating in the HOST Mode and this pin is config-

ured to function as the additional Receive Clock signal output pin, then the

XRT73L00 can be configured to update the data on the RPOS and RNEG output

pins on the falling edge of this clock signal.

31

RCLK1

O

Receive Clock Output pin 1:

This output pin is the Recovered Clock signal from the incoming line signal. The

receive section of the XRT73L00 outputs data via the RPOS and RNEG output

pins on the rising edge of this clock signal.

N

OTE

:

If the XRT73L00 is operating in the HOST Mode, the device can be con-

figured to update the data on the RPOS and RNEG output pins on the falling

edge of this clock signal.

32

RNEG

O

Receive Negative Pulse Output:

This output pin pulses “High” whenever the XRT73L00 has received a Negative

Polarity pulse in the incoming line signal at the RTIP/RRING inputs.

N

OTES

:

1. If the B3ZS/HDB3 Decoder is enabled, then the zero suppression pat-

terns in the incoming line signal (such as: "00V", "000V", "B0V", "B00V")

is not reflected at this output.

2. This output pin is inactive if the XRT73L00 has been configured to oper-

ate in the Single-Rail Mode.

33

RPOS

O

Receive Positive Pulse Output:

This output pin pulses “High” whenever the XRT73L00 has received a Positive

Polarity pulse in the incoming line signal at the RTIP/RRING inputs.

N

OTE

:

If the B3ZS/HDB3 Decoder is enabled, then the zero suppression pat-

terns in the incoming line signal (such as: "00V", "000V", "B0V", "B00V") is not

reflected at this output.

34

ICT

I

In-Circuit Test Input:

Setting this input pin “Low” causes all digital and analog outputs to go into a

high-impedance state in order to permit in-circuit testing. Set this pin “High” for

normal operation.

N

OTE

:

This pin is internally pulled “High”.

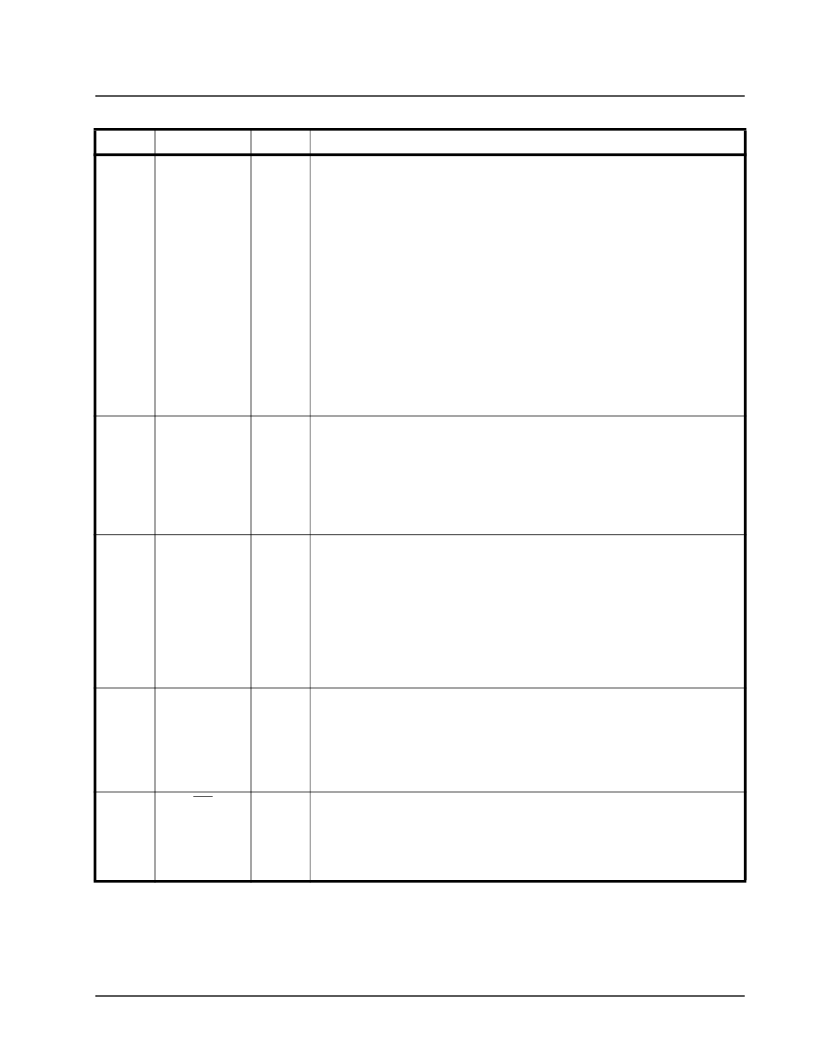

PIN DESCRIPTION

P

IN

#

S

YMBOL

T

YPE

D

ESCRIPTION

相關PDF資料 |

PDF描述 |

|---|---|

| XRT73LC00 | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73LC00IV | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L00 | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L00A | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L00AIV | E3/DS3/STS-1 LINE INTERFACE UNIT |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XRT73L03IVS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| XRT73L04A | 制造商:EXAR 制造商全稱:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L04AIV | 制造商:EXAR 制造商全稱:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L04B | 制造商:EXAR 制造商全稱:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L04BES | 功能描述:網(wǎng)絡控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。