- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1976 > XR19L212IL48-F (Exar Corporation)IC UART/TXRX RS232 48QFN PDF資料下載

參數(shù)資料

| 型號: | XR19L212IL48-F |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 30/52頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC UART/TXRX RS232 48QFN |

| 標(biāo)準(zhǔn)包裝: | 260 |

| 特點(diǎn): | * |

| 通道數(shù): | 2,DUART |

| FIFO's: | 64 字節(jié) |

| 規(guī)程: | RS232 |

| 電源電壓: | 3.3 V ~ 5.5 V |

| 帶自動(dòng)流量控制功能: | 是 |

| 帶IrDA 編碼器/解碼器: | 是 |

| 帶故障啟動(dòng)位檢測功能: | 是 |

| 帶調(diào)制解調(diào)器控制功能: | 是 |

| 帶CMOS: | 是 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-VFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 48-QFN-EP(7x7) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

XR19L212

36

TWO CHANNEL INTEGRATED UART AND RS-232 TRANSCEIVER

REV. 1.0.1

4.15

Device Revision Register (DREV) - Read Only

This register contains the device revision information. For example, 0x01 means revision A. Prior to reading

this register, DLL and DLM should be set to 0x00 (DLD = 0xXX).

4.16

Trigger Level Register (TRG) - Write-Only

User Programmable Transmit/Receive Trigger Level Register. If both the TX and RX trigger levels are used,

the TX trigger levels must be set before the RX trigger levels.

TRG[7:0]: Trigger Level Register

These bits are used to program desired trigger levels when trigger Table-D is selected. FCTR bit-7 selects

between programming the RX Trigger Level (a logic 0) and the TX Trigger Level (a logic 1).

4.17

RX/TX FIFO Level Count Register (FC) - Read-Only

This register is accessible when LCR = 0xBF. Note that this register is not identical to the FIFO Level Count

Register which is located in the general register set when FCTR bit-6 = 1 (Scratchpad Register Swap). It is

suggested to read the FIFO Level Count Register at the Scratchpad Register location when FCTR bit-6 = 1.

See Table 12.

FC[7:0]: RX/TX FIFO Level Count

Receive/Transmit FIFO Level Count. Number of characters in Receiver FIFO (FCTR[7] = 0) or Transmitter

FIFO (FCTR[7] = 1) can be read via this register. Reading this register is not recommended when transmitting

or receiving data.

4.18

Feature Control Register (FCTR) - Read/Write

FCTR[1:0]: RTS Hysteresis

User selectable RTS# hysteresis levels for hardware flow control application. After reset, these bits are set to

“0” to select the next trigger level for hardware flow control. See Table 13 for more details.

FCTR[2]: IrDa RX Inversion

Logic 0 = Select RX input as encoded IrDa data (Idle state will be LOW).

Logic 1 = Select RX input as inverted encoded IrDa data (Idle state will be HIGH).

FCTR[3]: Reserved

For proper functionality, this bit should be a logic 0.

FCTR[5:4]: Transmit/Receive Trigger Table Select

See Table 10 for more details.

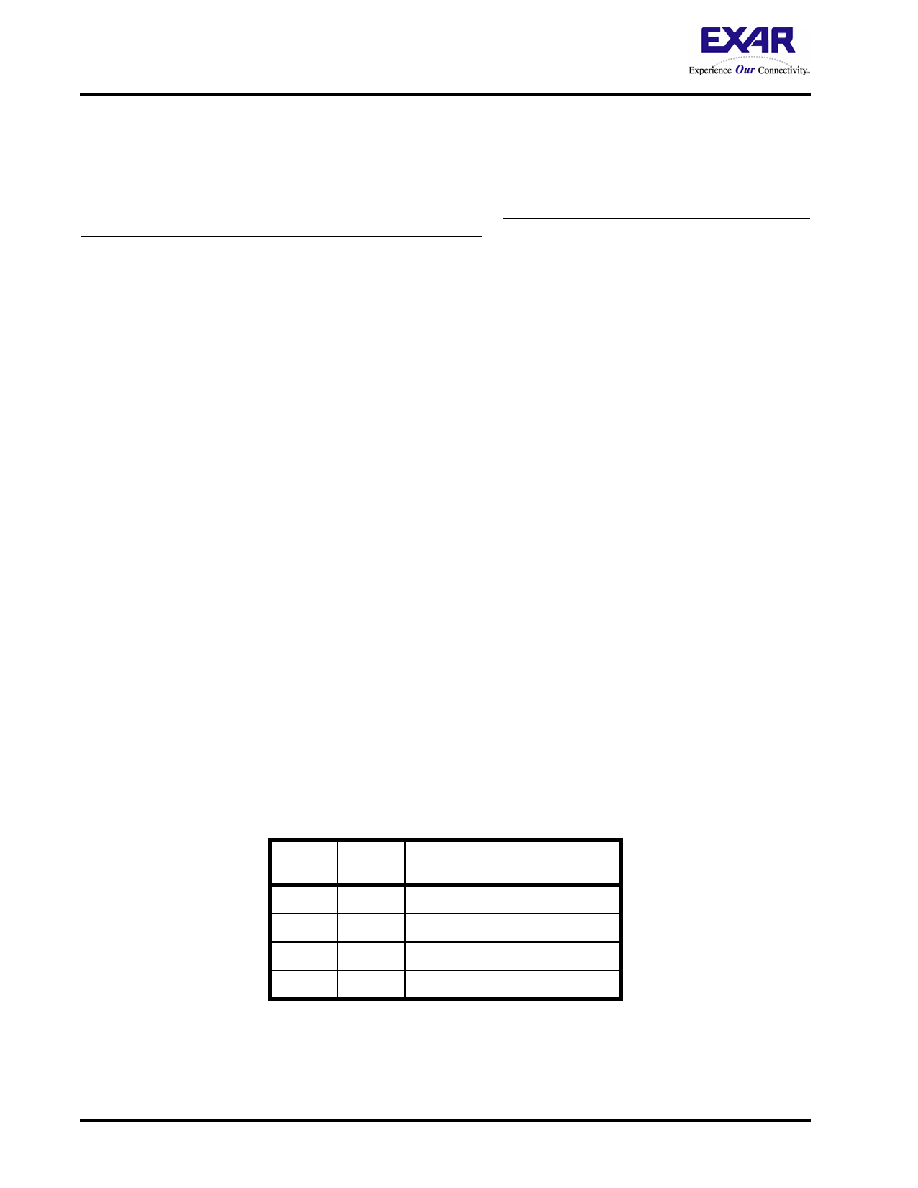

TABLE 14: TRIGGER TABLE SELECT

FCTR

BIT-5

FCTR

BIT-4

TABLE

0

Table-A (TX/RX)

0

1

Table-B (TX/RX)

1

0

Table-C (TX/RX)

1

Table-D (TX/RX)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR19L220IL40-F | IC UART/TXRX RS232 40QFN |

| XR19L222IL64-F | IC UART/TXRX RS232 64QFN |

| XR19L400IL40-F | IC UART/TXRX RS485 40QFN |

| XR19L402IL48-F | IC UART/TXRX RS485 48QFN |

| XR20M1170IL24TR-F | IC UART FIFO I2C/SPI 64B 24QFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR19L212IL48TR-F | 制造商:Exar Corporation 功能描述:UART 2-CH 64Byte FIFO 5V 48-Pin QFN EP T/R 制造商:Exar Corporation 功能描述:XR19L212IL48TR-F |

| XR19L220 | 制造商:EXAR 制造商全稱:EXAR 功能描述:SINGLE CHANNEL INTEGRATED UART AND RS-232 TRANSCEIVER |

| XR19L220_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:SINGLE CHANNEL INTEGRATED UART AND RS-232 TRANSCEIVER |

| XR19L220IL40 | 制造商:EXAR 制造商全稱:EXAR 功能描述:SINGLE CHANNEL INTEGRATED UART AND RS-232 TRANSCEIVER |

| XR19L220IL40-0A-EB | 功能描述:界面開發(fā)工具 Supports L220 40 pin QFN, ISA Interface RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。