- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄16523 > XR16V2652IL-0B-EB (Exar Corporation)EVAL BOARD FOR V2652 32QFN PDF資料下載

參數(shù)資料

| 型號(hào): | XR16V2652IL-0B-EB |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 27/48頁(yè) |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR V2652 32QFN |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

XR16V2652

33

REV. 1.0.2

HIGH PERFORMANCE DUART WITH 32-BYTE FIFO

AFR[0]: Concurrent Write Mode

When this bit is set, the CPU can write concurrently to the same register in both UARTs. This function is

intended to reduce the dual UART initialization time. It can be used by the CPU when both channels are

initialized to the same state. The external CPU can set or clear this bit by accessing either register set. When

this bit is set, the channel select pin still selects the channel to be accessed during read operations. The user

should ensure that LCR Bit-7 of both channels are in the same state before executing a concurrent write to the

registers at address 0, 1, or 2.

Logic 0 = No concurrent write (default).

Logic 1 = Register set A and B are written concurrently with a single external CPU I/O write operation.

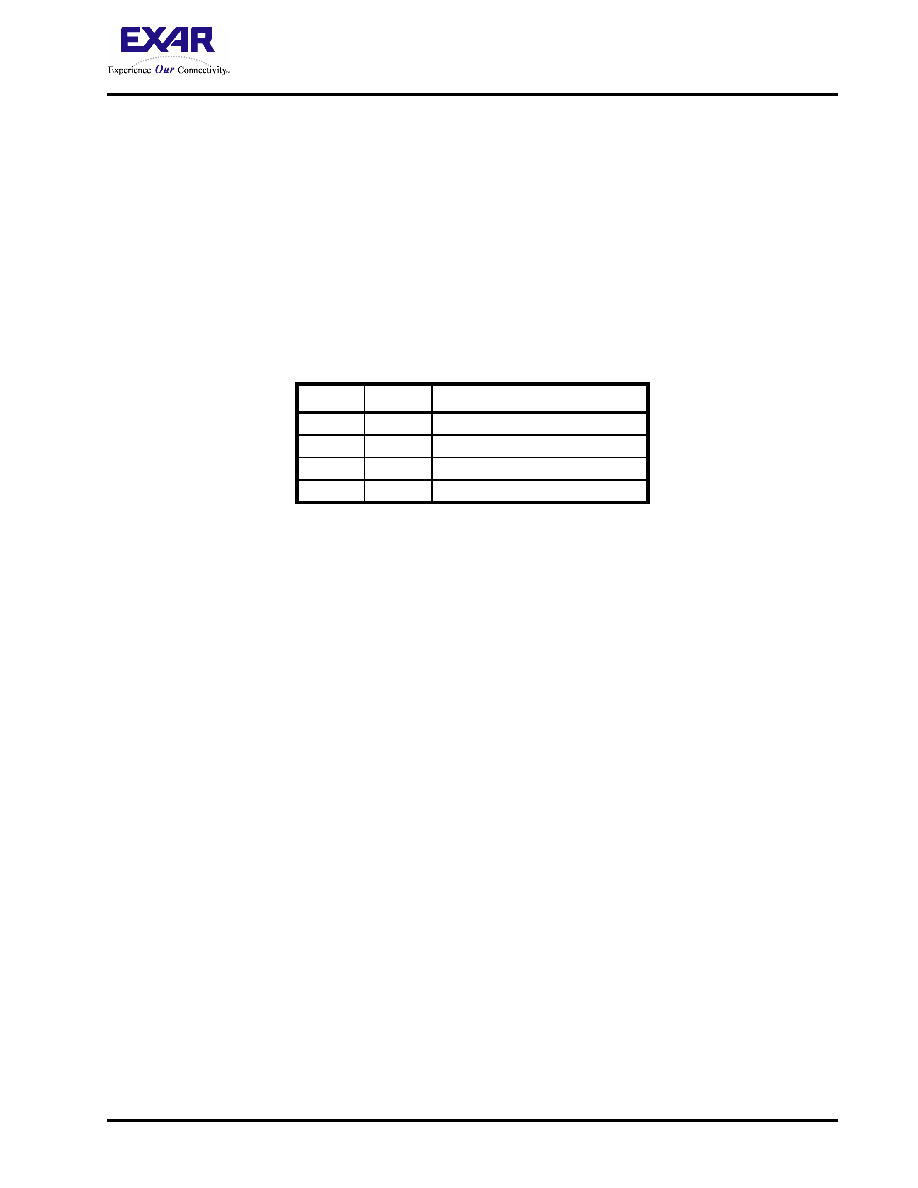

AFR[2:1]: MF# Output Select

These bits select a signal function for output on the MF# A/B pins. These signal function are described as:

OP2#, BAUDOUT#, or RXRDY#. Only one signal function can be selected at a time.

AFR[7:3]: Reserved

All are initialized to logic 0.

4.13

Device Identification Register (DVID) - Read Only

This register contains the device ID (0x06 for XR16V2652). Prior to reading this register, DLL and DLM should

be set to 0x00 (DLD = 0xXX).

4.14

Device Revision Register (DREV) - Read Only

This register contains the device revision information. For example, 0x01 means revision A. Prior to reading

this register, DLL and DLM should be set to 0x00 (DLD = 0xXX).

4.15

Enhanced Feature Register (EFR)

Enhanced features are enabled or disabled using this register. Bit 0-3 provide single or dual consecutive

character software flow control selection (see Table 14). When the Xon1 and Xon2 and Xoff1 and Xoff2 modes

are selected, the double 8-bit words are concatenated into two sequential characters. Caution: note that

whenever changing the TX or RX flow control bits, always reset all bits back to logic 0 (disable) before

programming a new setting.

BIT-2

BIT-1

MF# FUNCTION

0

OP2# (default)

0

1

BAUDOUT#

1

0

RXRDY#

1

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5022-392J | INDUCTOR 3.90UH 5% TOLERANCE SMD |

| GSM11DRTN-S13 | CONN EDGECARD 22POS .156 EXTEND |

| RCM10DTKI-S288 | CONN EDGECARD 20POS .156 EXTEND |

| A3DDB-1636G | IDC CABLE- AKR16B/AE16G/AKR16B |

| MCP1316T-29LE/OT | IC SUPERVISOR 2.90V P-P SOT23-5 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16V2652IL32 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:HIGH PERFORMANCE DUART WITH 32-BYTE FIFO |

| XR16V2652IL-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V2652ILTR-F | 制造商:Exar Corporation 功能描述:UART 2-CH 32Byte FIFO 2.5V/3.3V 32-Pin QFN EP T/R 制造商:Exar Corporation 功能描述:XR16V2652ILTR-F |

| XR16V2750 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

| XR16V2750_07 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。