- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4210 > XCV812E-6BG560C (Xilinx Inc)IC FPGA 1.8V C-TEMP 560-MBGA PDF資料下載

參數(shù)資料

| 型號: | XCV812E-6BG560C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 32/118頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 1.8V C-TEMP 560-MBGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB數(shù): | 4704 |

| 邏輯元件/單元數(shù): | 21168 |

| RAM 位總計: | 1146880 |

| 輸入/輸出數(shù): | 404 |

| 門數(shù): | 254016 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 560-LBGA,金屬 |

| 供應(yīng)商設(shè)備封裝: | 560-MBGA(42.5x42.5) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

Module 2 of 4

DS025-2 (v3.0) March 21, 2014

16

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

either asserted or de-asserted. Otherwise an abort is

initiated, as described below.

2.

Drive data onto D[7:0]. Note that to avoid contention,

the data source should not be enabled while CS is Low

and WRITE is High. Similarly, while WRITE is High, no

more that one CS should be asserted.

3.

At the rising edge of CCLK: If BUSY is Low, the data is

accepted on this clock. If BUSY is High (from a previous

write), the data is not accepted. Acceptance instead

occurs on the first clock after BUSY goes Low, and the

data must be held until this has happened.

4.

Repeat steps 2 and 3 until all the data has been sent.

5.

De-assert CS and WRITE.

A flowchart for the write operation appears in Figure 18.

Note that if CCLK is slower than fCCNH, the FPGA never

asserts BUSY, In this case, the above handshake is unnec-

essary, and data can simply be entered into the FPGA every

CCLK cycle.

Abort

During a given assertion of CS, the user cannot switch from

a write to a read, or vice-versa. This action causes the cur-

rent packet command to be aborted. The device remains

BUSY until the aborted operation has completed. Following

an abort, data is assumed to be unaligned to word boundar-

ies, and the FPGA requires a new synchronization word

prior to accepting any new packets.

To initiate an abort during a write operation, de-assert

WRITE. At the rising edge of CCLK, an abort is initiated, as

shown in Figure 19.

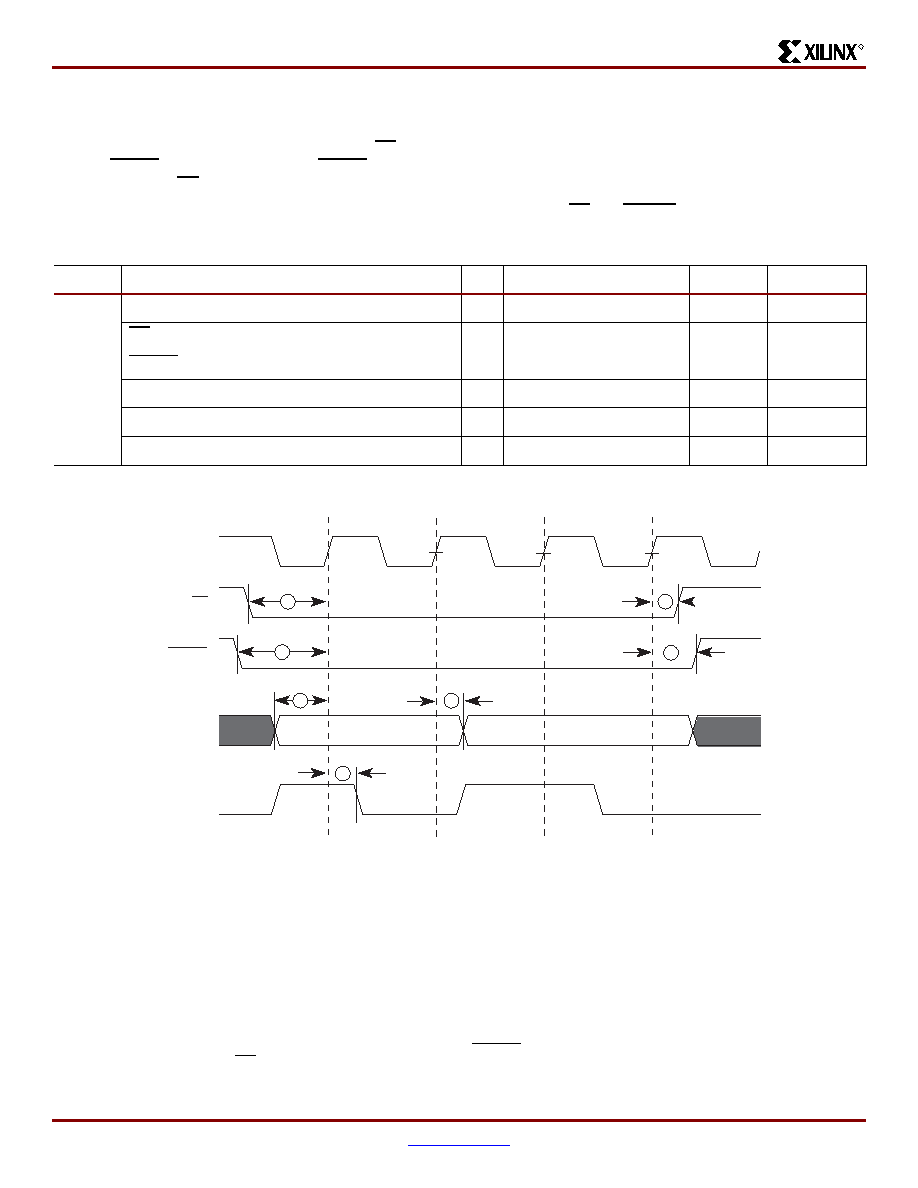

Table 11:

SelectMAP Write Timing Characteristics

Description

Symbol

Values

Units

CCLK

D0-7 Setup/Hold

1/2

TSMDCC/TSMCCD

5.0 / 1.7

ns, min

CS Setup/Hold

3/4

TSMCSCC/TSMCCCS

7.0 / 1.7

ns, min

WRITE Setup/Hold

5/6

TSMCCW/TSMWCC

7.0 / 1.7

ns, min

BUSY Propagation Delay

7

TSMCKBY

12.0

ns, max

Maximum Frequency

FCC

66

MHz, max

Maximum Frequency with no handshake

FCCNH

50

MHz, max

Figure 17: Write Operations

DS022_45_071702

CCLK

No Write

Write

No Write

Write

DATA[0:7]

CS

WRITE

3

5

BUSY

4

6

7

1

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMC19DREF-S13 | CONN EDGECARD 38POS .100 EXTEND |

| XC6VLX240T-1FF1156C | IC FPGA VIRTEX 6 241K 1156FFBGA |

| ACB60DHAS | CONN EDGECARD 120PS R/A .050 DIP |

| XC6VLX195T-1FF784I | IC FPGA VIRTEX-6LXT 784FFBGA |

| HMC60DRTI-S93 | CONN EDGECARD 120PS DIP .100 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV812E-6BG560I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6BG676C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6BG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6BG900C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6BG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。