- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374985 > XC3S1000-4FG676I (XILINX INC) Spartan-3 FPGA Family : Complete Data Sheet PDF資料下載

參數(shù)資料

| 型號: | XC3S1000-4FG676I |

| 廠商: | XILINX INC |

| 元件分類: | FPGA |

| 英文描述: | Spartan-3 FPGA Family : Complete Data Sheet |

| 中文描述: | FPGA, 1920 CLBS, 1000000 GATES, 630 MHz, PBGA676 |

| 封裝: | 27 X 27 MM, FBGA-676 |

| 文件頁數(shù): | 11/192頁 |

| 文件大小: | 1555K |

| 代理商: | XC3S1000-4FG676I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁

Spartan-3 1.2V FPGA Family: Functional Description

4

www.xilinx.com

1-800-255-7778

DS099-2 (v1.2) July 11, 2003

Advance Product Specification

40

R

Pull-Up and Pull-Down Resistors

The optional pull-up and pull-down resistors are intended to

establish High and Low levels, respectively, at unused I/Os.

The weak pull-up resistor optionally connects each IOB pad

to V

CCO

. A weak pull-down resistor optionally connects

each pad to GND. These resistors are placed in a design

using the PULLUP and PULLDOWN symbols in a sche-

matic, respectively. They can also be instantiated as com-

ponents, set as constraints or passed as attributes in HDL

code. These resistors can also be selected for all unused

I/O using the Bitstream Generator (BitGen) option Unused-

Pin. A Low logic level on HSWAP_EN activates the pull-up

resistors on all I/Os during configuration.

Weak-Keeper Circuit

Each I/O has an optional weak-keeper circuit that retains

the last logic level on a line after all drivers have been turned

off. This is useful to keep bus lines from floating when all

connected drivers are in a high-impedance state. This func-

tion is placed in a design using the KEEPER symbol.

Pull-up and pull-down resistors override the weak-keeper

circuit.

ESD Protection

Clamp diodes protect all device pads against damage from

Electro-Static Discharge (ESD) as well as excessive voltage

transients. Each I/O has two clamp diodes: One diode

extends P-to-N from the pad to V

CCO

and a second diode

extends N-to-P from the pad to GND. During operation,

these diodes are normally biased in the off state. These

clamp diodes are always connected to the pad, regardless

of the signal standard selected. The presence of diodes lim-

its the ability of Spartan-3 I/Os to tolerate high signal volt-

ages. The V

IN

absolute maximum rating in

Table 1

in

Module 3:

DC and Switching Characteristics

specifies the

voltage range that I/Os can tolerate.

Slew Rate Control and Drive Strength

Two options, FAST and SLOW, control the output slew rate.

The FAST option supports output switching at a high rate.

The SLOW option reduces bus transients. These options are

only available when using one of the LVCMOS or LVTTL

standards, which also provide up to seven different levels of

current drive strength: 2, 4, 6, 8, 12, 16, and 24 mA. Choos-

ing the appropriate drive strength level is yet another means

to minimize bus transients.

Table 3

shows the drive strengths that the LVCMOS and

LVTTL standards support. The Fast option is indicated by

appending an "F" attribute after the output buffer symbol

OBUF or the bidirectional buffer symbol IOBUF. The Slow

option appends an "S" attribute. The drive strength in milliam-

peres follows the slew rate attribute. For example,

OBUF_LVCMOS18_S_6 or IOBUF_LVCMOS25_F_16.

Boundary-Scan Capability

All Spartan-3 IOBs support boundary-scan testing compat-

ible with IEEE 1149.1 standards. See

Boundary-Scan

(JTAG) Mode

, page 36

for more information.

SelectIO

Signal Standards

The IOBs support 17 different single-ended signal stan-

dards, as listed in

Table 4

. Furthermore, the majority of

IOBs can be used in specific pairs supporting any of six dif-

ferential signal standards, as shown in

Table 5

. The desired

standard is selected by placing the appropriate I/O library

symbol or component into the FPGA design. For example,

the symbol named IOBUF_LVCMOS15_F_8 represents a

bidirectional I/O to which the 1.5V LVCMOS signal standard

has been assigned. The slew rate and current drive are set

to Fast and 8 mA, respectively.

Together with placing the appropriate I/O symbol, two exter-

nally applied voltage levels, V

CCO

and V

REF

select the

desired signal standard. The V

CCO

lines provide current to

the output driver. The voltage on these lines determines the

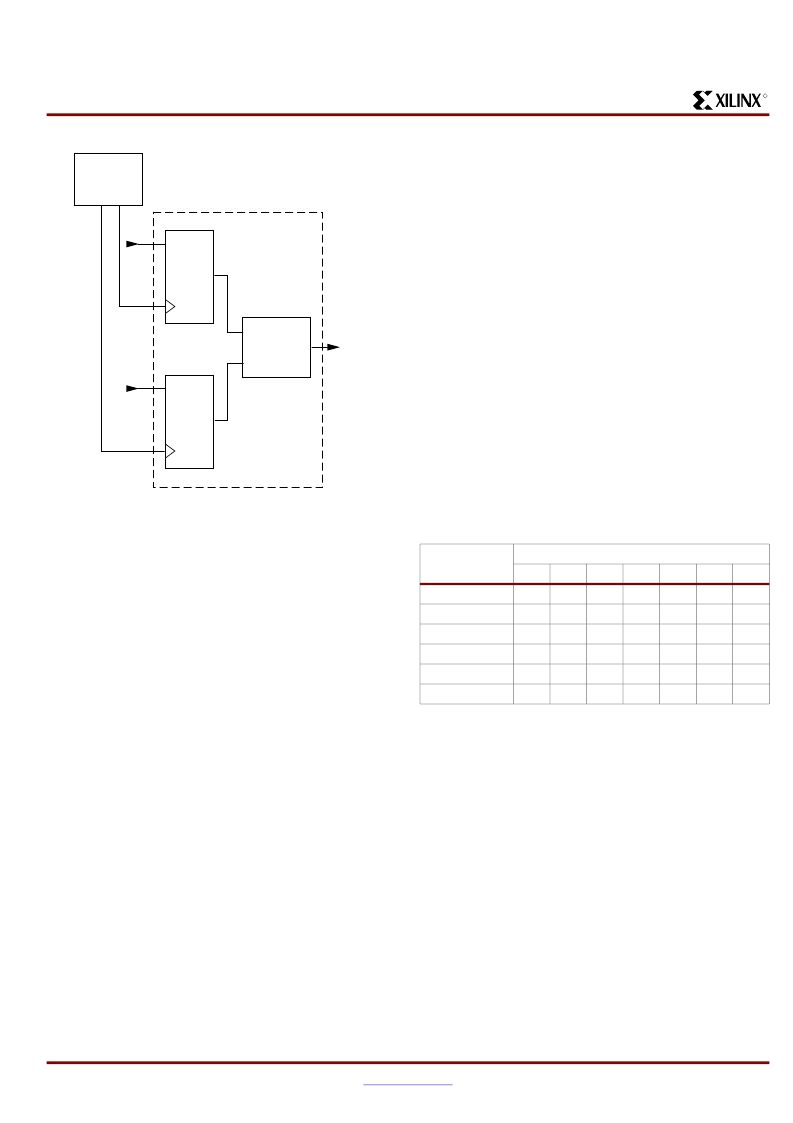

Figure 2:

Clocking the DDR Register

D1

CLK1

DDR MUX

DCM

Q1

FDDR

D2

CLK2

Q2

180 0

DS099-2_02_070303

Q

Table 3:

Programmable Output Drive Current

Signal

Standard

LVCMOS12

LVCMOS15

LVCMOS18

LVCMOS25

LVCMOS33

LVTTL

Current Drive (mA)

6

8

3

-

3

3

3

3

3

3

3

3

3

3

2

3

3

3

3

3

3

4

3

3

3

3

3

3

12

-

3

3

3

3

3

16

-

-

3

3

3

3

24

-

-

-

3

3

3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3S1000-4FG900C | Spartan-3 FPGA Family : Complete Data Sheet |

| XC3S1000-4FG900I | Spartan-3 FPGA Family : Complete Data Sheet |

| XC3S1000-4FT256C | Spartan-3 FPGA Family : Complete Data Sheet |

| XC3S1000-4FT256I | Spartan-3 FPGA Family : Complete Data Sheet |

| XC3S1000-4TQ144C | Spartan-3 FPGA Family: Complete Data Sheet |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S1000-4FG900C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA Family : Complete Data Sheet |

| XC3S1000-4FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1000-4FGG320C | 功能描述:SPARTAN-3A FPGA 1M STD 320-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S1000-4FGG320I | 功能描述:IC SPARTAN-3A FPGA 1M 320-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S1000-4FGG456C | 功能描述:IC SPARTAN-3 FPGA 1M 456-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計:221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。