- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359452 > VV5404 (Electronic Theatre Controls, Inc.) CIF FORMAT DIGITAL IMAGE SENSOR PDF資料下載

參數(shù)資料

| 型號: | VV5404 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | CIF FORMAT DIGITAL IMAGE SENSOR |

| 中文描述: | CIF格式的數(shù)字圖像傳感器 |

| 文件頁數(shù): | 5/54頁 |

| 文件大小: | 786K |

| 代理商: | VV5404 |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

VV5404 & VV6404

CD5404-6404F-A

5/54

1. Fast QCK: the falling edge of the clock qualifies the nibble data irrespective of whether it is the most or the least

significant nibble.

2. Slow QCK: the rising edge of the clock qualifies the most significant nibbles while the falling edge of the clock

qualifies the least significant nibbles.

The FST can be enabled/disabled via the serial interface.

OEB tri-states all 4 databus lines, D[3:0], the qualification clock, QCK and the frame start signal, FST.

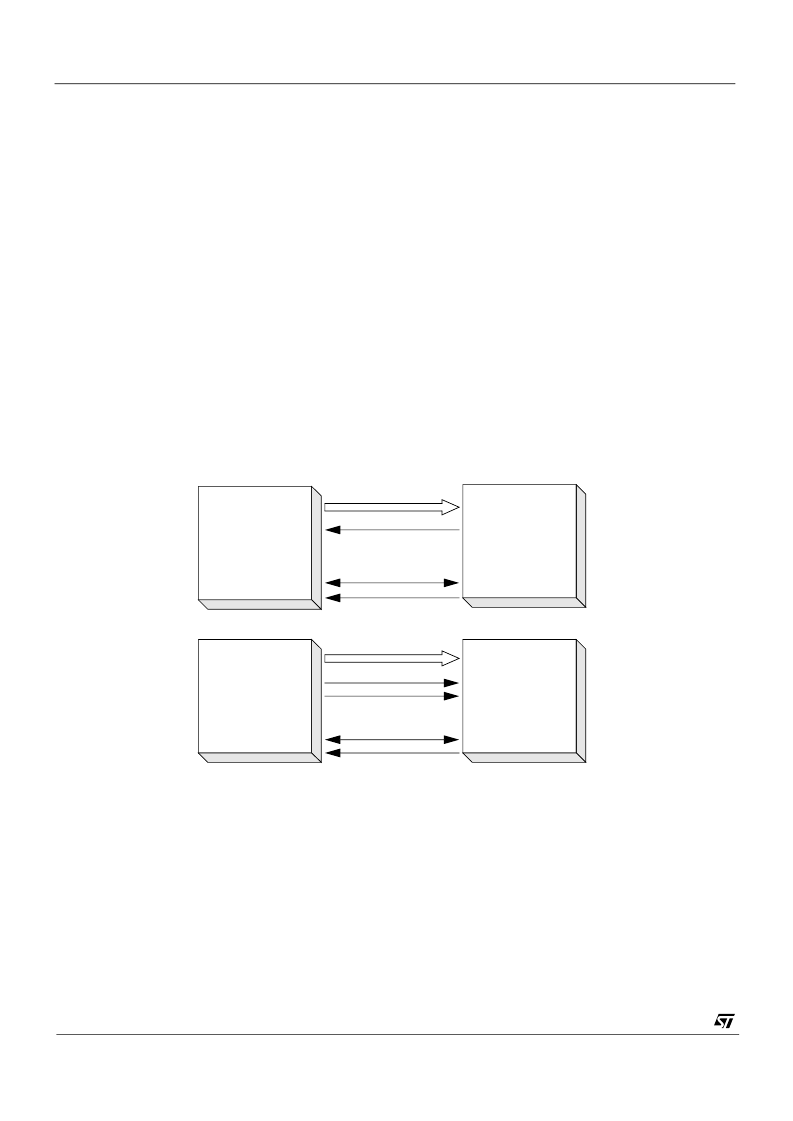

There are 3 main ways of interfacing to the VV5404 or VV6404 sensor based on the above signals:

1. The processor capturing the data (or colour co-processor for VV6404) supplies the sensor clock, CKI, and uses

the embedded control sequences to synchronise with the frame and line level timings. Thus the processor and

sensor are running off derivatives of the same fundamental clock (4 fsc - 14.31818 MHz). To allow the receiver

to determine the best sampling position of the video data, during its power-up sequence the sensor outputs a

101010... sequence on each of its databus lines for the video processor to lock on to.

2. The video processor uses a free-running QCK supplied by the sensor to sample the incoming video data

stream. The embedded control sequences are used to synchronise the frame and line level timings. A crystal is

used to generate the clock for the sensor.

3. The video processor uses FST and the data only mode for QCK to synchronise to the incoming video data. Pri-

marily intended for interfacing to frame grabbers.

The 2-wire serial interface provides complete control over how the sensor is setup and run. Exposure and gain values

are programmed via this interface. Section 5. defines the communications protocol and the register map of all the

locations which can be accessed via the serial interface.

Using the first two interface options outlined above it is possible to control the sensor and receive video data via a 9-

wire cable between the sensor and the video processor/colour-processor.

1. A 4-wire data bus (D[3:0]) for sending both video data and embedded timing references.

2. A 2-wire serial interface (SDA,SCL).

3. The clock for the sensor or QCK from the sensor.

4. VCC and GND power lines.

The various image read-out and frame rate options are detailed in Sections 2 and 3 respectively.

Figure 2 : Interfacing Options

SDA

SCL

D[3:0]

CLKI

Sensor

Colour

Co-processor

(processor)

SDA

SCL

D[3:0]

QCK

Sensor

Colour

Co-processor

(processor)

FST

相關PDF資料 |

PDF描述 |

|---|---|

| VV5410 | Mono and Colour Digital Video CMOS Image Sensors |

| VV5430C001 | Monochrome Analog Output CMOS Image Sensors |

| VV5430 | Integrated CMOS Image Sensor with support for ADC and external control via serial interface |

| VV6410C036 | DUAL-MODE DIGITAL CAMERA CHIPSET |

| VV6410 | XTAL MTL T/H HC49/US |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VV5404C001 | 制造商:STMicroelectronics 功能描述:MONO SENSOR - Bulk |

| VV5410 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Mono and Colour Digital Video CMOS Image Sensors |

| VV5410C036 | 制造商:STMicroelectronics 功能描述:IMAGE SENSOR MONOCHROME CMOS 352X288PIXELS 36CLCC - Bulk |

| VV5430 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Integrated CMOS Image Sensor with support for ADC and external control via serial interface |

| VV5430C001 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Monochrome Analog Output CMOS Image Sensors |

發(fā)布緊急采購,3分鐘左右您將得到回復。