- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359352 > VCT3801A (MICRONAS SEMICONDUCTOR HOLDING AG) Video/Controller/Teletext IC Family PDF資料下載

參數(shù)資料

| 型號(hào): | VCT3801A |

| 廠(chǎng)商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Video/Controller/Teletext IC Family |

| 中文描述: | 視頻/控制/圖文電視IC系列 |

| 文件頁(yè)數(shù): | 22/172頁(yè) |

| 文件大小: | 2243K |

| 代理商: | VCT3801A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)

VCT 38xxA

ADVANCE INFORMATION

22

Micronas

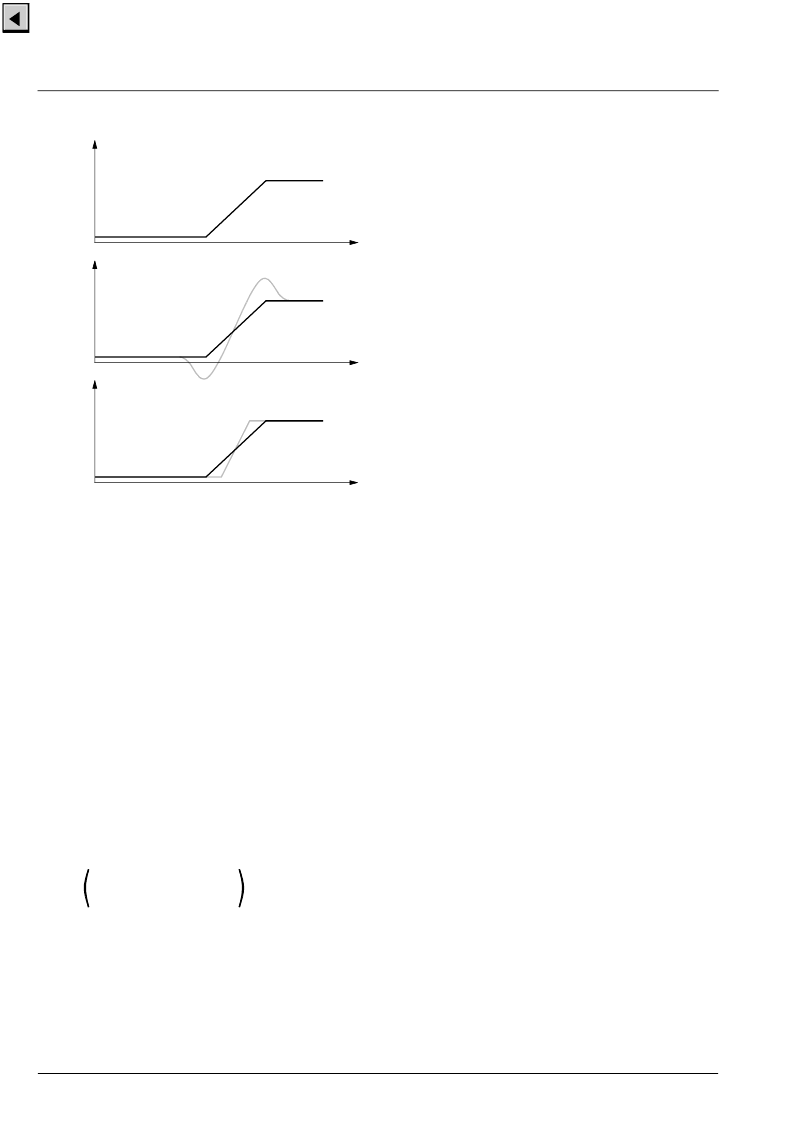

Fig. 2–16:

Digital color transient improvement

2.10.8.Inverse Matrix

A 6-multiplier matrix transcodes the C

r

and C

b

signals

to R-Y, B-Y, and G-Y. The multipliers are also used to

adjust color saturation in the range of 0 to 2. The coef-

ficients are signed and have a resolution of 9 bits.

There are separate matrix coefficients for main and

side pictures. The matrix computes:

R

Y

=

MR1*C

b

+

MR2*C

r

G

Y

=

MG1*C

b

+

MR2*C

r

B

Y

=

MB1*C

b

+

MR2*C

r

The initialization values for the matrix are computed

from the standard ITUR (CCIR) matrix:

For a contrast setting of CTM

+

32, the matrix values

are scaled by a factor of 64 (see Table 2–4 on

page 34).

2.10.9.RGB Processing

After adding the post-processed luma, the digital RGB

signals are limited to 10 bits. Three multipliers are

used to digitally adjust the white drive. Using the same

multipliers an average beam current limiter is imple-

mented (see Section 2.11.1. on page 25).

2.10.10.OSD Color Look-up Table

The VCT 38xxA has five input lines for an OSD signal.

This signal forms a 5-bit address for a color look-up

table (CLUT). The CLUT is a memory with 32 words

where each word holds a RGB value.

Bits 0 to 3 (bit 4

=

0) form the addresses for the ROM

part of the OSD, which generates full RGB signals (bit

0 to 2) and half-contrast RGB signals (bit 3).

Bit 4 addresses the RAM part of the OSD with 16

freely programmable colors, addressable with bit 0 to

3. The programming is done via the I

2

C bus.

The amplitude of the CLUT output signals can be

adjusted separately for R, G, and B via the I

2

C bus.

The switchover between video RGB and OSD RGB is

done via the priority decoder.

2.10.11.Picture Frame Generator

When the picture does not fill the total screen (height

or width too small) it is surrounded with black areas.

These areas (and more) can be colored with the pic-

ture frame generator. This is done by switching over

the RGB signal from the matrix to the signal from the

OSD color look-up table.

The width of each area (left, right, upper, lower) can be

adjusted separately. The generator starts on the right,

respectively lower side of the screen and stops on the

left, respectively upper side of the screen. This means,

it runs during horizontal, respectively vertical flyback.

The color of the complete border can be stored in the

programmable OSD color look-up table in a separate

address. The format is 3 x 4-bit RGB. The contrast can

be adjusted separately.

The picture frame generator includes a priority master

circuit. Its priority is programmable and the border is

generated only if the priority is higher than the priority

of the other sources (video/OSD). Therefore, the bor-

der can be underlay or overlay depending on the pic-

ture source.

a) C

r

C

b

input of DTI

b) C

r

C

b

input

+

correction signal

c) sharpened and limited C

r

C

b

t

t

t

C

r

in

C

b

in

a)

b)

Ampl.

C

r

out

C

b

out

c)

R

G

B

=

1

1

1

0

0.345

1.773

1.402

0.713

0

Y

C

b

C

r

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VCU2133 | High-Speed coder/decoder IC |

| VCX2150A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCX2154A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCXO-105N | VCXO |

| VCXO-199 | VCXO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VCT3802A | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3803A | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3804A | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3811A | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3831A | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Video/Controller/Teletext IC Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。