- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383985 > USB97CFDC-MN (STANDARD MICROSYSTEMS CORP) USB FLOPPY DISK CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | USB97CFDC-MN |

| 廠商: | STANDARD MICROSYSTEMS CORP |

| 元件分類: | 存儲(chǔ)控制器/管理單元 |

| 英文描述: | USB FLOPPY DISK CONTROLLER |

| 中文描述: | 1 Mbps, FLOPPY DISK DRIVE CONTROLLER, PQFP100 |

| 封裝: | 12 X 12 MM, TQFP-100 |

| 文件頁數(shù): | 31/59頁 |

| 文件大?。?/td> | 385K |

| 代理商: | USB97CFDC-MN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

SMSC DS – USB97C201

Page 31

Rev. 03/25/2002

PRELIMINARY

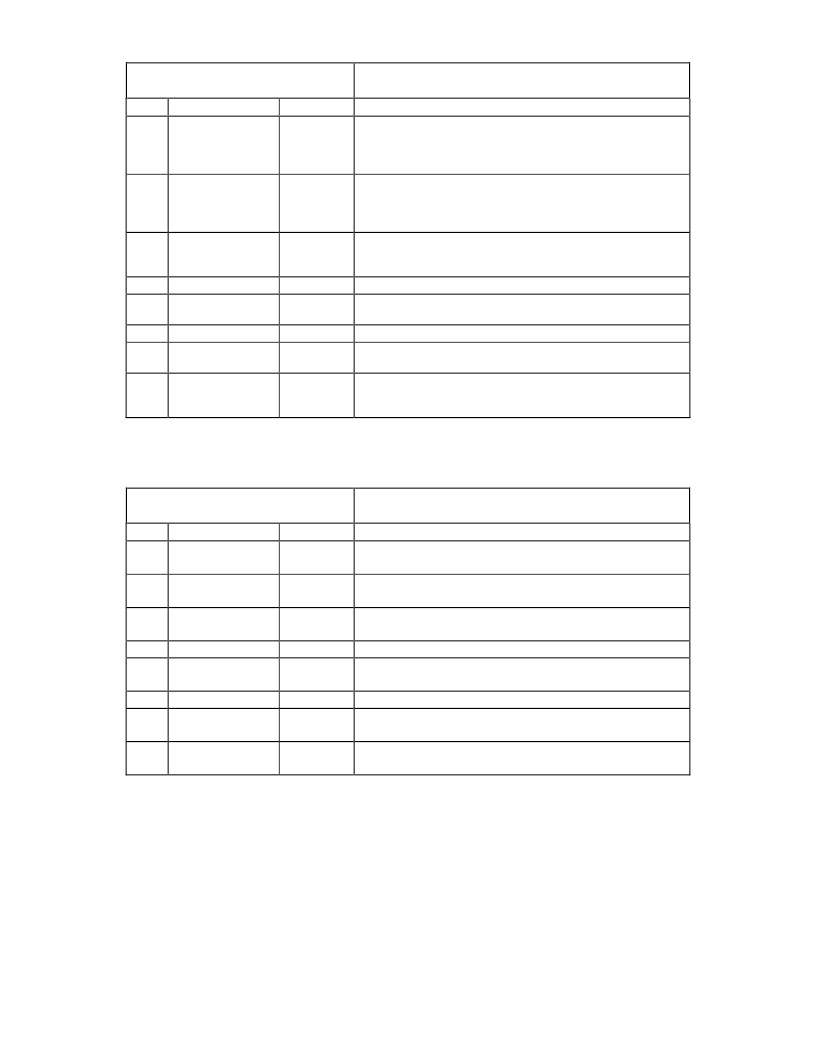

Table 28 – SIE Status Register

SIE_STAT

(0xB0 - RESET=0x00)

NAME

SET_STALL

SIE STATUS REGISTER

DESCRIPTION

BIT

[7]

R/W

R/W

Set to “1” if a SET_FEATURE_ENDPOINT_HALT command

is received on any endpoint by the SIE. Which endpoint is

STALLed can be determined by examining their CTL

registers.

Set to “1” if a CLEAR_FEATURE_ENDPOINT_HALT

command is received on any endpoint by the SIE. Which

endpoint’s STALL condition is cleared can be determined

by examining their CTL registers.

Set to “1” if a SET_CONFIGURATION command is received

on endpoint 0 by the SIE and the resulting configuration is

set and reported in the USB_CONFIG register.

This read only bit always returns the value of “0”.

Set to “1” if a SET_INTERFACE command is received on

endpoint 0 by the SIE.

This read only bit always returns the value of “0”.

Set to “1” if a SET_FEATURE_REMOTE_WAKE_UP

command is received on endpoint 0 by the SIE.

Set

to

CLEAR_FEATURE_ENDPOINT_REMOTE_WAKE_UP

command is received on endpoint 0 by the SIE.

6

CLR_STALL

R/W

5

SET_CONF

R/W

4

3

Reserved

SET_INTF

R

R/W

2

1

Reserved

SET_REMWU

R-

R/W

0

CLR_REMWU

R/W

“1”

if

a

Note:

These bits are masked by the SIE_MSK register and OR’d to drive the INT3 interrupt line into the 8051 core.

They may be cleared writing a “1” to the bit location.

Table 29 – SIE Status Mask Register

SIE_MSK

(0xAE - RESET=0xFF)

NAME

SET_STALL

SIE STATUS MASK REGISTER

DESCRIPTION

1= Disable interrupt generation.

0= Enable interrupt generation.

1= Disable interrupt generation.

0= Enable interrupt generation.

1= Disable interrupt generation.

0= Enable interrupt generation.

This read only bit always returns the value of “1”.

1= Disable interrupt generation.

0= Enable interrupt generation.

This read only bit always returns the value of “1”.

1= Disable interrupt generation.

0= Enable interrupt generation.

1= Disable interrupt generation.

0= Enable interrupt generation.

BIT

[7]

R/W

R/W

6

CLR_STALL

R/W

5

SET_CONF

R/W

4

3

Reserved

SET_INTF

R

R/W

2

1

Reserved

SET_REMWU

R

R/W

0

CLR_REMWU

R/W

Note:

The mask bits do not prevent the status in the SIE_STAT register from being set, only from driving the INT3

line of the 8051 core high.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| USB97C202 | ATA/ATAPI CONTROLLER |

| USB97C202-MN-02 | ATA/ATAPI CONTROLLER |

| USB97C223 | capacitor Selection for Internal Regulator Output Pins |

| USB97C243 | capacitor Selection for Internal Regulator Output Pins |

| USB97CFDC | USB FLOPPY DISK CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| USB-A(M)-A(F)-1M-BEIGE | 制造商:SMART CABLE 功能描述: |

| USB-A-001A | 制造商:YAMAICHI 制造商全稱:Yamaichi Electronics Co., Ltd. 功能描述:Universal Serial Bus, Type A - 90° Receptacle |

| USB-A-001A-30 | 制造商:YAMAICHI 制造商全稱:Yamaichi Electronics Co., Ltd. 功能描述:Universal Serial Bus, Type A - 90° Receptacle |

| USB-A-002A | 制造商:YAMAICHI 制造商全稱:Yamaichi Electronics Co., Ltd. 功能描述:Universal Serial Bus, Type A - 90° Receptacle |

| USB-A-002A-30 | 制造商:YAMAICHI 制造商全稱:Yamaichi Electronics Co., Ltd. 功能描述:Universal Serial Bus, Type A - 90° Receptacle |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。