- 您現(xiàn)在的位置:買賣IC網 > PDF目錄359758 > TSC251G2DXXX-L16CED IC CYCLONE III FPGA 80K 780FBGA PDF資料下載

參數(shù)資料

| 型號: | TSC251G2DXXX-L16CED |

| 英文描述: | IC CYCLONE III FPGA 80K 780FBGA |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 16/63頁 |

| 文件大小: | 878K |

| 代理商: | TSC251G2DXXX-L16CED |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

Rev. A - May 7, 1999

16

TSC80251G2D

7. Instruction Set Summary

This section contains tables that summarize the instruction set. For each instruction there is a short description, its

length in bytes, and its execution time in states (one state time is equal to two system clock cycles). There are

two concurrent processes limiting the effective instruction throughput:

G

Instruction Fetch

G

Instruction Execution

Table 20 to Table 34 assume code executing from on-chip memory, then the CPU is fetching 16-bit at a time and

this is never limiting the execution speed.

If the code is fetched from external memory, a pre-fetch queue will store instructions ahead of execution to optimize

the memory bandwidth usage when slower instructions are executed. However, the effective speed may be limited

depending on the average size of instructions (for the considered section of the program flow). The maximum

average instruction throughput is provided by Table 14 depending on the external memory configuration (from

Page Mode to Non-Page Mode and the maximum number of wait states). If the average size of instructions is not

an integer, the maximum effective throughput is found by pondering the number of states for the neighbor integer

values.

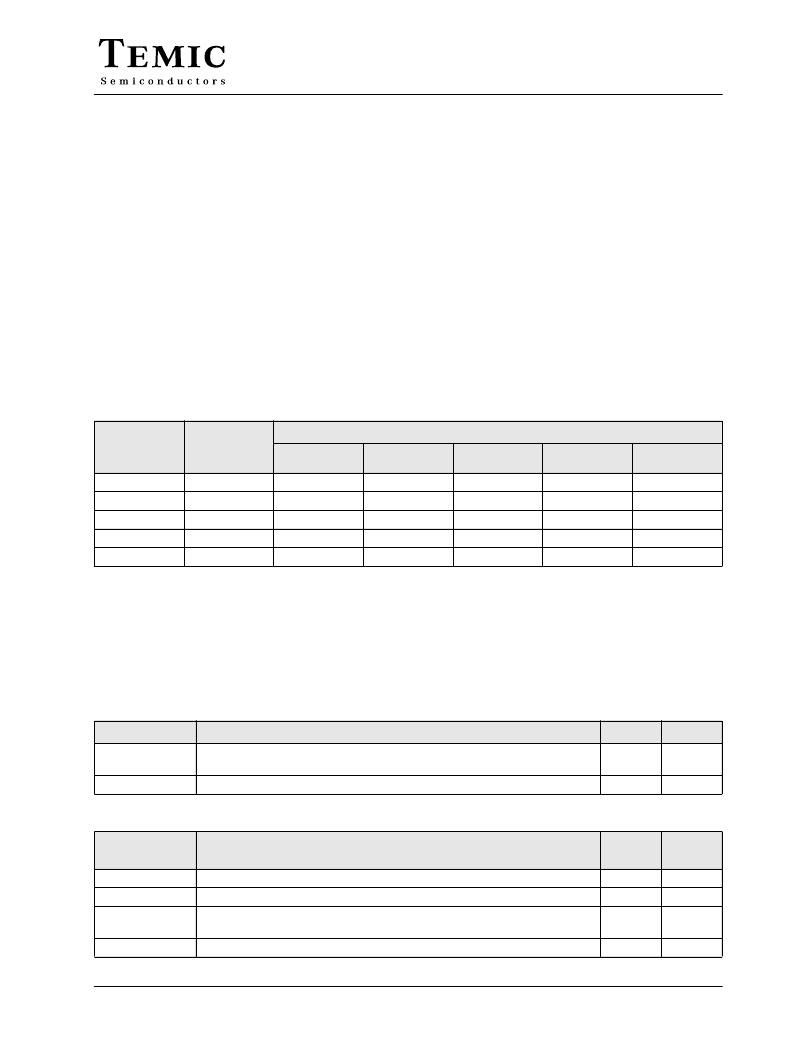

Table 14. Minimum Number of States per Instruction for given Average Sizes

If the average execution time of the considered instructions is larger than the number of states given by Table 14,

this larger value will prevail as the limiting factor. Otherwise, the value from Table 14 must be taken. This is

providing a fair estimation of the execution speed but only the actual code execution can provide the final value.

7.1 Notation for Instruction Operands

Table 15 to Table 19 provide notation for Instruction Operands.

Table 15. Notation for Direct Addressing

Table 16. Notation for Immediate Addressing

Average size of

Instructions

(bytes)

Page Mode

(states)

Non-Page Mode (states)

0 Wait State

1 Wait State

2 Wait States

3 Wait States

4 Wait States

1

1

2

3

4

5

6

2

2

4

6

8

10

12

3

3

6

9

12

15

18

4

4

8

12

16

20

24

5

5

10

15

20

25

30

Direct Address

Description

C251

C51

dir8

A direct 8-bit address. This can be a memory address (00h-7Fh) or a SFR address (80h-

FFh). It is a byte (default), word or double word depending on the other operand.

dir16

A 16-bit memory address (00:0000h-00:FFFFh) used in direct addressing.

Immediate

Address

Description

C251

C51

#data

An 8-bit constant that is immediately addressed in an instruction

#data16

A 16-bit constant that is immediately addressed in an instruction

#0data16

#1data16

A 32-bit constant that is immediately addressed in an instruction. The upper word is filled

with zeros (#0data16) or ones (#1data16).

#short

A constant, equal to 1, 2, or 4, that is immediately addressed in an instruction.

相關PDF資料 |

PDF描述 |

|---|---|

| TSC87251G2D-24CED | Process/Temperature Controller; Control Operation:Auto/Manual, Ramp/Soak, Stand By, Valve Positioning; Control Output Relay Rating:264 VAC / 2 A; Control Type:On/Off, PID; Controller Output Type 1:Relay RoHS Compliant: NA |

| T1005 | TELECOMMUNICATIONS PRODUCTS |

| T1005NL | TELECOMMUNICATIONS PRODUCTS |

| T1006 | TELECOMMUNICATIONS PRODUCTS |

| T1006NL | TELECOMMUNICATIONS PRODUCTS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TSC-25A | 制造商:RIEDON 制造商全稱:Riedon Powertron 功能描述:Tubular Power Wirewound Resistors |

| TSC-25B | 制造商:RIEDON 制造商全稱:Riedon Powertron 功能描述:Tubular Power Wirewound Resistors |

| TSC2620 | 制造商:TRACOPOWER 制造商全稱:TRACO Electronic AG 功能描述:DC/DC Converter |

| TSC2622 | 制造商:TRACOPOWER 制造商全稱:TRACO Electronic AG 功能描述:DC/DC Converter |

發(fā)布緊急采購,3分鐘左右您將得到回復。