- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383964 > TPU3035 (MICRONAS SEMICONDUCTOR HOLDING AG) CONNECTOR ACCESSORY PDF資料下載

參數(shù)資料

| 型號: | TPU3035 |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | CONNECTOR ACCESSORY |

| 中文描述: | 連接器附件 |

| 文件頁數(shù): | 58/73頁 |

| 文件大小: | 1183K |

| 代理商: | TPU3035 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當(dāng)前第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

PRELIMINARY DATA SHEET

TPU 3035, TPU 3040

MICRONAS INTERMETALL

58

026F H

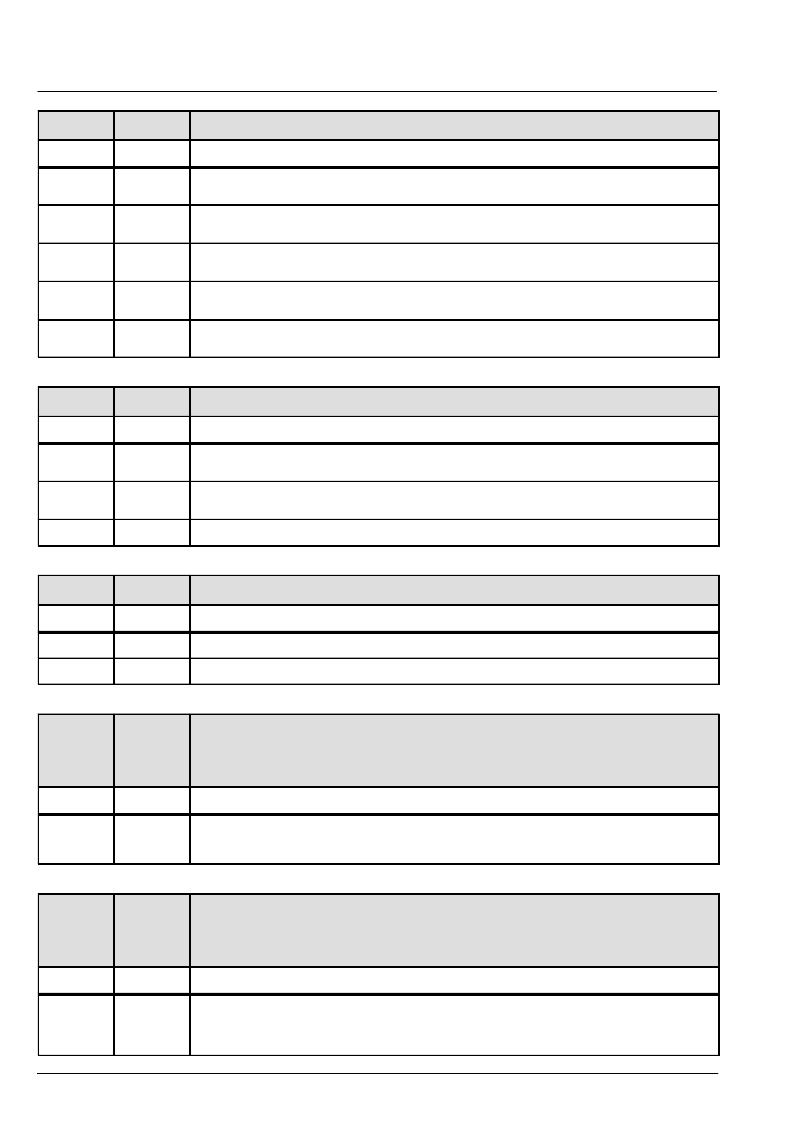

Write

DISPLAY MODE 3

Bit

Reset

Function

7

1

1 = 10 pixel/character

0 = 8 pixel/character

6

0

1 = double dot size in vertical direction

0 = normal dot size in vertical direction

(OSD layer only)

5

0

1 = double dot size in horizontal direction

0 = normal dot size in horizontal direction

(OSD layer only)

4

0

1 = black colors replaced by transparent & shadow

0 = black colors displayed black

(OSD layer only)

3 to 0

F H

4-bit value defining delay of horizontal start for both layers (in pixel)

delay = mod

16

(character_width – 2 – value)

(leftmost position should not be used!)

0270 H

Write

DISPLAY MODE 4

Bit

Reset

Function

2

0

1 = boxing enable

0 = boxing disable

1

0

1 = reveal enable

0 = reveal disable

0

0

This bit is taken as flash clock for the WST layer, the frequency should be around 6 Hz.

0273 H

Write

DISPLAY MODE 5

Bit

Reset

Function

4

0

WST layer scan line counter preset (LSB for zoom mode)

3 to 0

0

WST layer scan line counter preset

0280 H

0283 H

0286 H

0289 H

R/W

DRAM DISPLAY POINTER LOW

DRAM SLICER POINTER LOW

DRAM CPU WRITE POINTER LOW

DRAM CPU READ POINTER LOW

Bit

Reset

Function

7 to 0

–

8 least significant bits of 21 bit address pointer

12 LSBs of 21 bit address pointer are running with autoincrement

read value is only specified when pointer is not incrementing

0281 H

0284 H

0287 H

028A H

R/W

DRAM DISPLAY POINTER MEDIUM

DRAM SLICER POINTER MEDIUM

DRAM CPU WRITE POINTER MEDIUM

DRAM CPU READ POINTER MEDIUM

Bit

Reset

Function

all

–

8 medium bits of 21 bit address pointer

12 LSBs of 21 bit address pointer are running with autoincrement

read value is only specified when pointer is not incrementing

writing this register clears all lower bits of related pointer

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPU3040 | CONNECTOR ACCESSORY |

| TPU3041 | CONNECTOR ACCESSORY |

| TRF1121_07 | Dual VCO/PLL Synthesizer With IF Up-Converter |

| TRF1122_07 | 2.5-GHz Integrated Up-Converter |

| TRM7043 | OC-192 SR-2 Transmitter Module(OC-192 SR-2 發(fā)送器模塊) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPU3035(DIP40) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Consumer IC |

| TPU3035(PDIP40) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| TPU3035(PLCC44) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| TPU3035(PSDIP52) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| TPU304 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | JFET | P-CHANNEL | 30MA I(DSS) | TO-226AA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。