- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371187 > TMPR28051 TMPR28051 STS-1/AU-3 (STM-0) Mapper Device Advisory for Version 5 of the Device PDF資料下載

參數(shù)資料

| 型號: | TMPR28051 |

| 英文描述: | TMPR28051 STS-1/AU-3 (STM-0) Mapper Device Advisory for Version 5 of the Device |

| 中文描述: | TMPR28051 STS-1/AU-3(的STM - 0)映射為版本的設(shè)備5設(shè)備咨詢 |

| 文件頁數(shù): | 73/90頁 |

| 文件大?。?/td> | 1090K |

| 代理商: | TMPR28051 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

Data Sheet

August 1999

TMPR28051 STS-1/AU-3 (STM-0) Mapper

59

Lucent Technologies Inc.

Microprocessor Interface Description

(continued)

Register Architecture Description

(continued)

Receive J1 Path Trace Bytes (0xC0—0xFF)

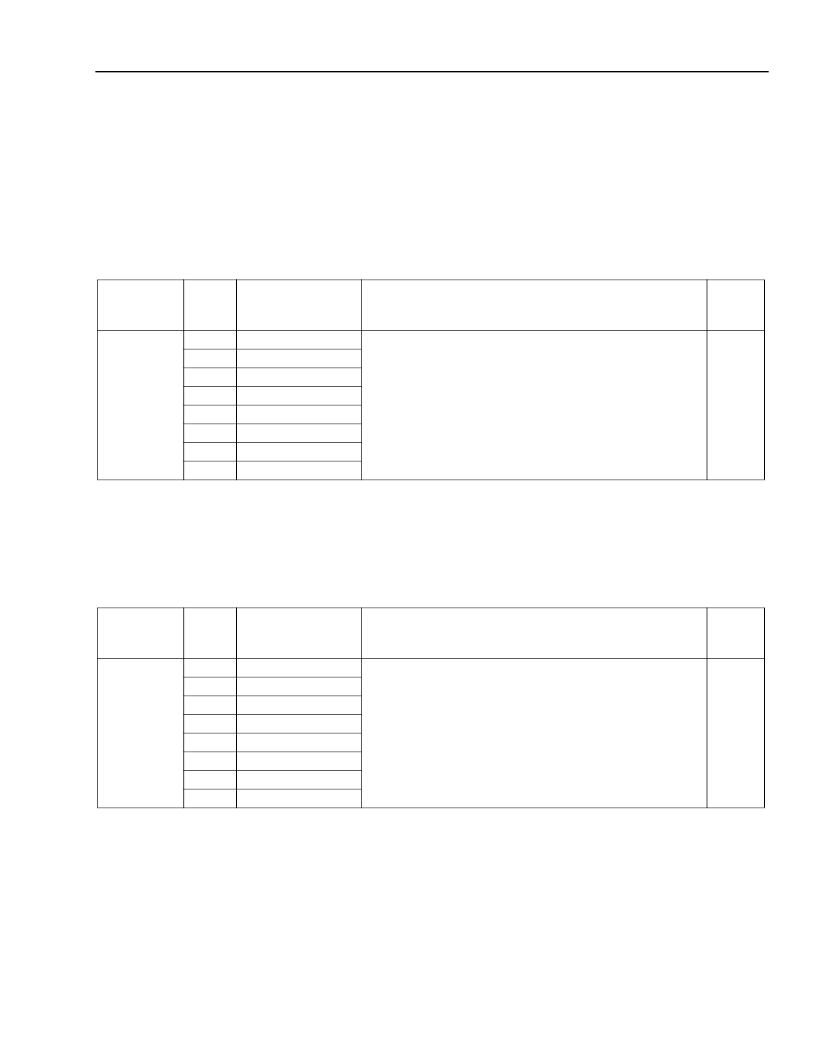

Table 31. Registers 0xC0—0xFF: Receive J1 Path Trace Bytes

Note:

Bits in registers 0xC0—0xFF can have one of four configurations, depending upon the setting of register

0xBF. When register 0xBF is set for BIP_CNTS = 0

and

REI_CNTS = 0

and

RJ1BYTE = 1, the bytes in reg-

isters 0xC0—0xFF are used to read the received 64 path trace bytes.

Transmit J1 Path Trace Bytes (0xC0—0xFF)

Table 32. Registers 0xC0—0xFF: Transmit J1 Path Trace Bytes

Note:

Bits in registers 0xC0—0xFF can have one of four configurations, depending upon the setting of register

0xBF. When register 0xBF is set for BIP_CNTS = 0

and

RJ1BYTE = 1

and

TJ1BYTE = 1, the bytes in regis-

ters 0xC0—0xFF are used to provision the transmit 64 path trace bytes.

Address

(Hex)

Bit #

Name

Function

Reset

Default

(Hex)

Value is

0.

0xC0—0xFF

7

6

5

4

3

2

1

0

RJ1BYTE7_[64:1]

RJ1BYTE6_[64:1]

RJ1BYTE5_[64:1]

RJ1BYTE4_[64:1]

RJ1BYTE3_[64:1]

RJ1BYTE2_[64:1]

RJ1BYTE1_[64:1]

RJ1BYTE0_[64:1]

The receive J1 path trace byte RJ1BYTE[7:0]_64 corre-

sponds to the first byte in the 64-byte sequence, while the

J1 path trace byte RJ1BYTE[7:0]_1 corresponds to the

last byte in the 64-byte sequence. These specified

receive J1 byte values are continuously written, modulo

64, into the 0xC0—0xFF registers. If any received byte

does not match the previously received byte for its loca-

tion, then TRACEER bit (bit 7) in register 0x03 is set to 1.

Address

(Hex)

Bit #

Name

Function

Reset

Default

(Hex)

Value is

0.

0xC0—0xFF

7

6

5

4

3

2

1

0

TJ1BYTE7_[64:1]

TJ1BYTE6_[64:1]

TJ1BYTE5_[64:1]

TJ1BYTE4_[64:1]

TJ1BYTE3_[64:1]

TJ1BYTE2_[64:1]

TJ1BYTE1_[64:1]

TJ1BYTE0_[64:1]

The transmit J1 path trace byte TJ1BYTE[7:0]_64 corre-

sponds to the first byte in the 64-byte sequence, while the

J1 path trace byte TJ1BYTE[7:0]_1 corresponds to the

last byte in the 64-byte sequence. These registers can be

written by the microprocessor.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMUX03155 | TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer |

| TMXF28155 | TMXF28155 Super Mapper 155/51 Mbits/s SONET/SDH x28/x21 DS1/E1 |

| TMXF84622 | TMXF84622 155 Mbits/s/622 Mbits/s Interface SONET/SDH x84/x63 Ultramapper |

| TN2-L-H-3V | SLIM POLARIZED RELAY |

| TN2-L-H-48V | SLIM POLARIZED RELAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMPR28051-3-SL5 | 制造商:AGERE 制造商全稱:AGERE 功能描述:TMPR28051 STS-1/AU-3 (STM-0) Mapper Device Advisory for Version 5 of the Device |

| TMPR28051-SL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET MAPPER|QFP|208PIN|PLASTIC |

| TMPR3904F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|QFP|208PIN|PLASTIC |

| TMPR3907F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|QFP|208PIN|PLASTIC |

| TMPR3911 | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:32-Bit TX System RISC TX39 Family |

發(fā)布緊急采購,3分鐘左右您將得到回復。