- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371187 > TMPR28051 TMPR28051 STS-1/AU-3 (STM-0) Mapper Device Advisory for Version 5 of the Device PDF資料下載

參數(shù)資料

| 型號: | TMPR28051 |

| 英文描述: | TMPR28051 STS-1/AU-3 (STM-0) Mapper Device Advisory for Version 5 of the Device |

| 中文描述: | TMPR28051 STS-1/AU-3(的STM - 0)映射為版本的設(shè)備5設(shè)備咨詢 |

| 文件頁數(shù): | 62/90頁 |

| 文件大?。?/td> | 1090K |

| 代理商: | TMPR28051 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁當(dāng)前第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

Data Sheet

August 1999

TMPR28051 STS-1/AU-3 (STM-0) Mapper

48

Lucent Technologies Inc.

Microprocessor Interface Description

(continued)

Register Architecture Description

(continued)

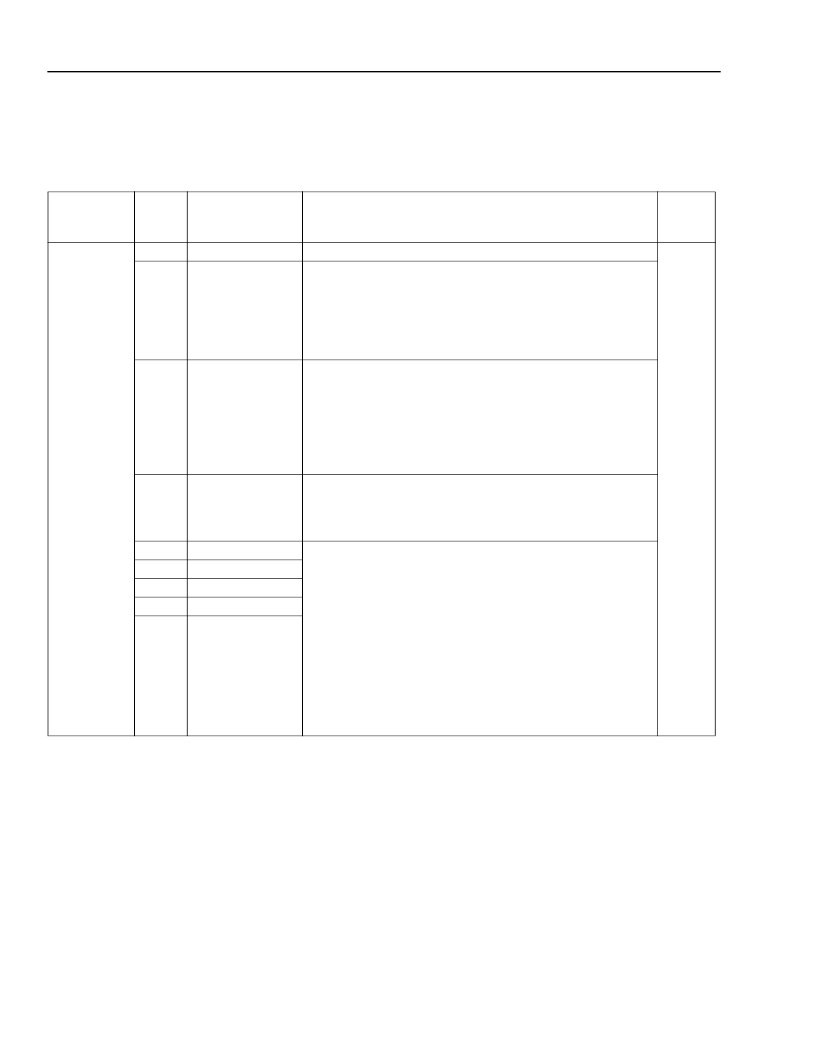

Table 16. Registers 0x17—0x32: DS1/E1 Insertion Selection

(continued)

Address

(Hex)

Bit #

Name

Function

Reset

Default

(Hex)

Value is

0.

0x2C—0x32

—

7

—

Registers 0x17—0x32 report DS1 conditions.

The DS1/E1AIS[1:21] and DS1AIS[22:28] bits report the

received DS1 AIS condition. When any of these bits is 1,

the corresponding DS1 input has an AIS condition. This

value represents the current received state. The AIS condi-

tion is not latched by these bits. The indication is reset

when the condition is no longer true.

The DS1/E1LOC[1:21] and DS1LOC[22:28] bits in bit 6

report the received DS1 loss of clock condition. When any

of these bits is 1, the corresponding DS1 input has a

received loss of clock condition. This value represents the

current received state. The loss of clock condition is not

latched by these bits. The indication is reset when the con-

dition is no longer true.

The DS1/E1LB[1:21] and DS1LB[22:28] bits in bit 5 are

used to force DS1 loopback from output to input. When any

of these bits is 1, the corresponding DS1 input is overwrit-

ten by the outgoing DS1 signal for that location.

DS1INS4_[22:28] The DS1/E1INS[4:0]_[1:21] and DS1INS[4:0]_[22:28] bits

in registers 0x17—0x32 are used to select the DS1 input

for the transmit VT1.5 slots. The DS1 selected corresponds

to the decimal value of the programmed 5 bits. If these bits

contain 00000, the device will insert unequipped into the

corresponding VT1.5 slot. If these bits contain 11101—

11110, the device will insert AIS-V into the corresponding

VT1.5 slot. Since the device defaults all 28 of these regis-

ters to the value 00000, all of the 28 VT1.5 slots begin

transmitting unequipped following reset. The value 11111

inserts the test pattern. Addresses 0x17—0x32 correspond

to VT1.5s as shown in Table 17, page 49.

DS1AIS[22:28]

6

DS1LOC[22:28]

5

DS1LB[22:28]

4

3

2

1

0

DS1INS3_[22:28]

DS1INS2_[22:28]

DS1INS1_[22:28]

DS1INS0_[22:28]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMUX03155 | TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer |

| TMXF28155 | TMXF28155 Super Mapper 155/51 Mbits/s SONET/SDH x28/x21 DS1/E1 |

| TMXF84622 | TMXF84622 155 Mbits/s/622 Mbits/s Interface SONET/SDH x84/x63 Ultramapper |

| TN2-L-H-3V | SLIM POLARIZED RELAY |

| TN2-L-H-48V | SLIM POLARIZED RELAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMPR28051-3-SL5 | 制造商:AGERE 制造商全稱:AGERE 功能描述:TMPR28051 STS-1/AU-3 (STM-0) Mapper Device Advisory for Version 5 of the Device |

| TMPR28051-SL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET MAPPER|QFP|208PIN|PLASTIC |

| TMPR3904F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|QFP|208PIN|PLASTIC |

| TMPR3907F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|QFP|208PIN|PLASTIC |

| TMPR3911 | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:32-Bit TX System RISC TX39 Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。