- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383959 > TMC2193KJC (FAIRCHILD SEMICONDUCTOR CORP) 10 Bit Encoder PDF資料下載

參數(shù)資料

| 型號(hào): | TMC2193KJC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類(lèi): | 消費(fèi)家電 |

| 英文描述: | 10 Bit Encoder |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | MQFP-100 |

| 文件頁(yè)數(shù): | 24/72頁(yè) |

| 文件大?。?/td> | 448K |

| 代理商: | TMC2193KJC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

TMC2193

PRODUCT SPECIFICATION

24

REV. 1.0 3/26/03

Subcarrier Synchronization

There are 5 modes of subcarrier synchronization in the

TMC2193, freerun, subcarrier reset, Genlock, DRS-lock and

Ancillary Data Control (ANC).

Freerun

At the rising edge of RESET the DDS starts to generate the

subcarrier reference and will continue to freerun the subcar-

rier. When setting the control register DDSRST is HIGH, the

TMC2193 will reset the DDS to the SYSPH value on the

next field 1, line 1 (line 4 for NTSC), pixel 1 occurrence and

will reset this bit to be LOW. This allows the encoder to start

with the correct SCH relationship. The phase of the subcar-

rier reference will drift over time since a 32 bit accumulator

has a error of

±

0.5 Hz when generating the subcarrier refer-

ence for NTSC 13.5 MHz.

Subcarrier Reset

At the rising edge of RESET the DDS starts to generate the

subcarrier reference and will reset the DDS to the SYSPH

value every field 1, line 1 (line 4 for NTSC), pixel 1 occur-

rence. This enables the encoder to maintain the proper SCH

relationship.

Genlock

The Genlock mode allows the TMC2193 to lock to a com-

posite reference when used in conjunction with the

TMC22071A Genlocking Video Digitizer. The TMC22071A

produces a genlock reference signal (GRS) which contains

field identification, PALODD status, relative phase and rela-

tive frequency of the composite reference. The GRS is sam-

pled on the CVBS bus 60 PXCK’s after the falling edge of

HSIN. The phase and frequency values are used to update

the DDS on a line to line basis, thus synchronizing the sub-

carrier to an external composite reference.

DRS-Lock

The DRS-Lock mode allows the TMC2193 to lock its com-

posite output to the decoded composite or S-video input of

the TMC22x5y. The TMC22x5y produces a decoder refer-

ence signal (DRS) which contains field identification, PAL-

ODD status, relative phase and relative frequency of the

composite or S-video input. The DRS is sampled on either

the CVBS bus or the PD port, depending on DRSSEL, 60

PXCK’s after the falling edge of HSIN. The phase and fre-

quency values are used to update the DDS on a line to line

basis, thus synchronizing the subcarrier to an external com-

posite reference.

Ancillary Data Control (ANC)

Subcarrier synchronization in ANC mode is covered in the

Ancillary Data Control section of this data sheet.

SCH Phase Error Correction

SCH refers to the timing relationship between the 50% point

of the leading edge of horizontal sync and the positive or

negative zero-crossing of the color burst subcarrier refer-

ence. SCH error is usually expressed in degrees of subcarrier

phase. In PAL, SCH is defined for line 1 of field 1, but since

there is no color burst on line 1, SCH is usually measured at

line 7 of field 1. The need to specify SCH relative to a partic-

ular line in PAL is due to the 25 Hz offset of PAL subcarrier

frequency. Since NTSC has no such 25 Hz offset, SCH

applies to all lines.

The SCH relationship is important in the TMC2193 when

two video sources are being combined or if the composite

video output is externally combined with another video

source. In these cases, improper SCH phasing will result in a

noticeable horizontal jump of one image with respect to

another and/or a change in hue proportional to the SCH error

between the two sources.

SCH phasing can be adjusted by modifying BURPH and

SYSPH values by equal amounts. SCH is advanced/delayed

by one degree by increasing/decreasing the value of BURPH

and SYSPH by approximately B6

h

. An SCH error of 15

o

is

corrected with SYSPH and BURPH offsets of AAA

h

.

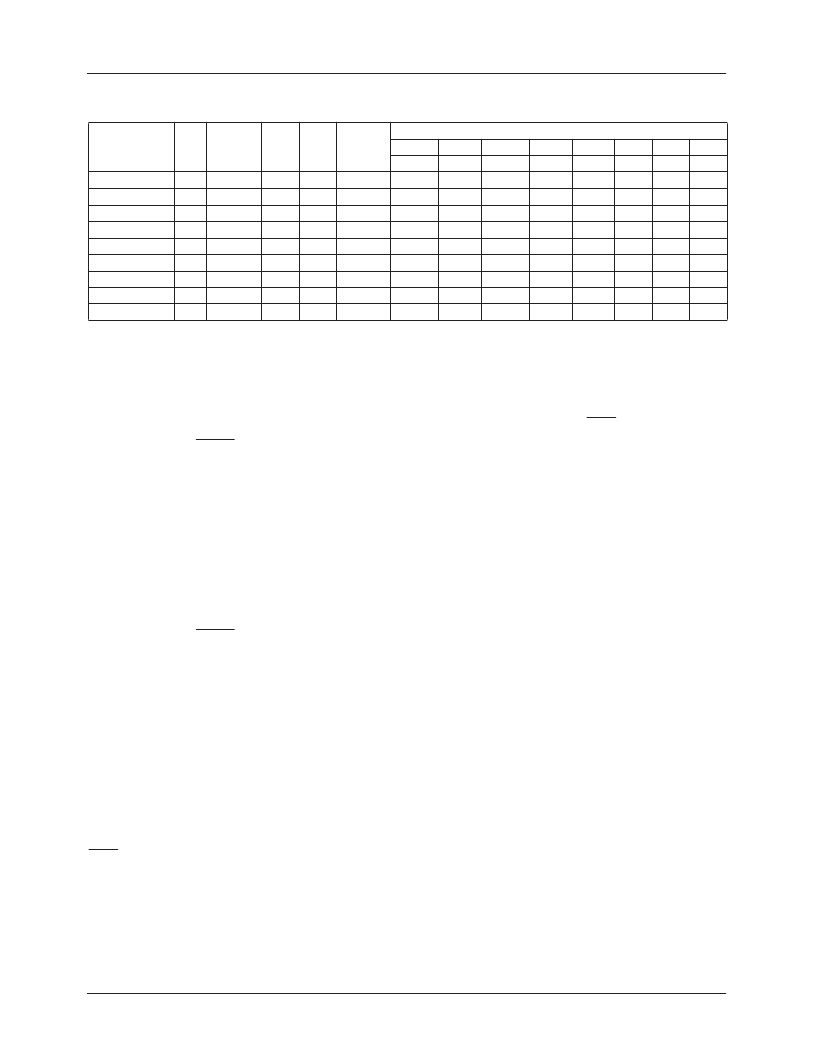

Table 14. Standard Subcarrier Parameters

Standard

Field

Rate

(Hz)

Horizontal

Freq.

(kHz)

Pixel

Rate

(Mpps)

PXCK

Freq.

(MHz)

Subcarrier

Freq.

(MHz)

Subcarrier Register (hex)

BURPHM BURPHL

SYSPHM

SYSPHL

FREQM

FREQ2

FREQ3 FREQL

47

46

45

44

43

42

41

40

NTSC sqr. pixel

59.94

15.734266

12.27

24.54

3.57954500

00

00

00

00

4A

AA

AA

AB

NTSC CCIR-601

59.94

15.734266

13.50

27.00

3.57954500

00

00

00

00

43

E0

F8

3E

NTSC 4x F

SC

59.94

15.734266

14.32

28.64

3.57954500

00

00

00

00

40

00

00

00

PAL sqr. pixel

50.00

15.625000

14.75

29.50

4.43361875

00

00

00

00

4C

F3

18

19

PAL CCIR-601

50.00

15.625000

13.50

27.00

4.43361875

00

00

00

00

54

13

15

96

PAL 15 Mpps

50.00

15.625000

15.00

30.00

4.43361875

00

00

00

00

4B

AA

C6

A1

PAL-M sqr.pixel

60.00

15.750000

12.50

25.01

3.57561149

00

00

00

00

49

45

00

51

PAL-M CCIR-601

60.00

15,750000

13.50

27.00

3.57561149

00

00

00

00

43

DF

3F

D7

PAL-M 4x F

SC

60.00

15,750000

14.30

28.60

3.57561149

00

00

00

00

40

10

66

F5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC2193 | 10 Bit Encoder |

| TMC22051AKHC | Circular Connector; No. of Contacts:11; Series:MS27484; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:18; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:18-11 RoHS Compliant: No |

| TMC22X5YA | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22052AKHC | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22053AKHC | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC22 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC22051 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC22051AKHC | 功能描述:多媒體雜項(xiàng) RoHS:否 制造商:Texas Instruments 類(lèi)型: 通道數(shù)量: 轉(zhuǎn)換速率:540 Mbps 分辨率: 封裝 / 箱體:SOIC-16 封裝:Tube |

| TMC22052AKHC | 制造商:FAIRCHILD 制造商全稱(chēng):Fairchild Semiconductor 功能描述:Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22053AKHC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。