- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98254 > TLV320AIC3110IRHBT (TEXAS INSTRUMENTS INC) AUDIO AMPLIFIER, PQCC32 PDF資料下載

參數(shù)資料

| 型號: | TLV320AIC3110IRHBT |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 音頻/視頻放大 |

| 英文描述: | AUDIO AMPLIFIER, PQCC32 |

| 封裝: | 5 X 5 MM, GREEN, PLASTIC, QFN-32 |

| 文件頁數(shù): | 91/126頁 |

| 文件大小: | 1528K |

| 代理商: | TLV320AIC3110IRHBT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁當(dāng)前第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

www.ti.com

SLAS647 – DECEMBER 2009

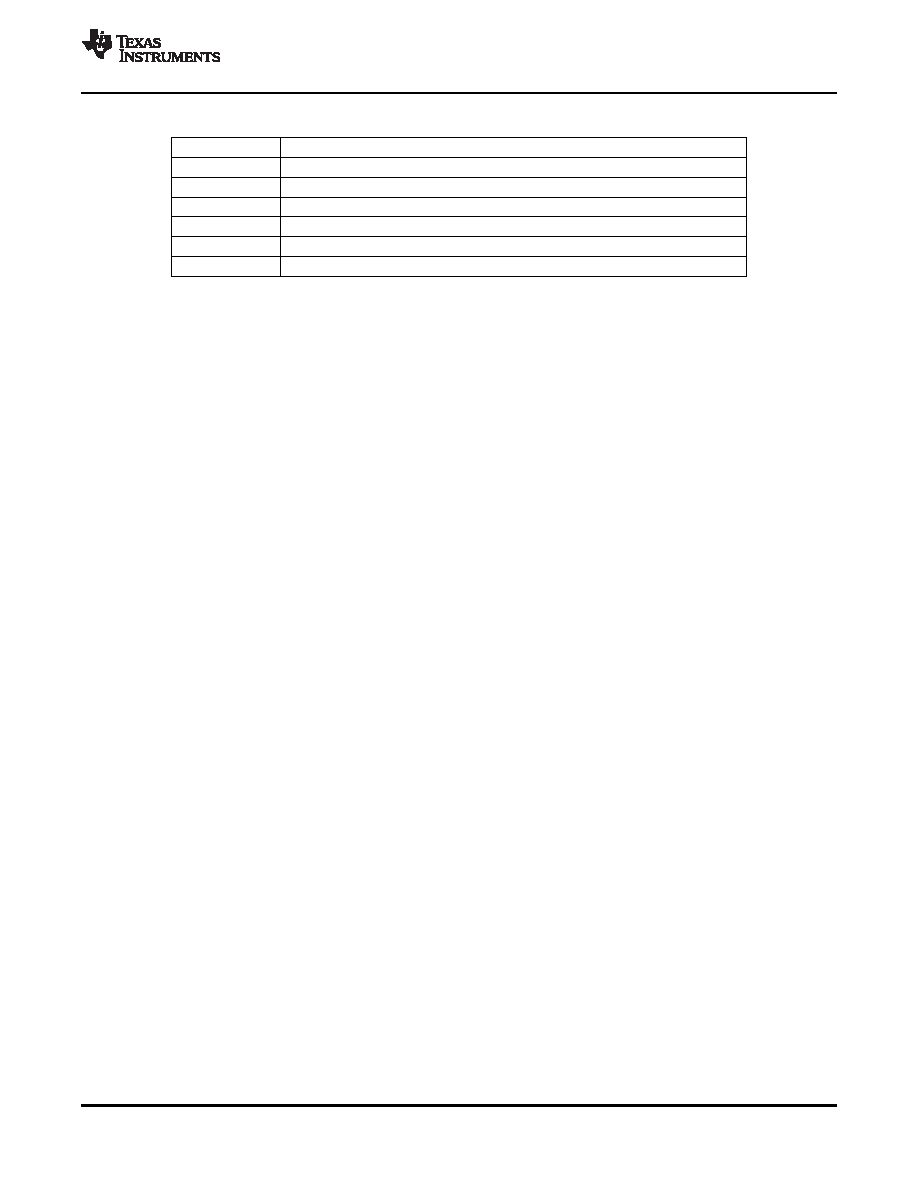

Table 5-40. CODEC CLKIN Clock Dividers

Divider

Bits

NDAC

Page 0 / register 11, bits D6–D0

MDAC

Page 0 / register 12, bits D6–D0

DOSR

Page 0 / register 13, bits D1–D0 and page 0 / register 14, bits D7–D0

NADC

Page 0 / register 18, bits D6–D0

MADC

Page 0 / register 19, bits D6–D0

AOSR

Page 0 / register 20, bits D7–D0

The DAC modulator is clocked by DAC_MOD_CLK. For proper power-up operation of the DAC channel,

these clocks must be enabled by configuring the NDAC and MDAC clock dividers (page 0 / register 11,

bit D7 = 1 and page 0 / register 12, bit D7 = 1). When the DAC channel is powered down, the device

internally initiates a power-down sequence for proper shutdown. During this shutdown sequence, the

NDAC and MDAC dividers must not be powered down, or else a proper low-power shutdown may not take

place. The user can read back the power-status flag at page 0 / register 37, bit D7 and page 0 /

register 37, bit D3. When both the flags indicate power down, the MDAC divider may be powered down,

followed by the NDAC divider. Note that when the ADC clock dividers are powered down, the ADC clock

is derived from the DAC clocks.

The ADC modulator is clocked by ADC_MOD_CLK. For proper power-up of the ADC channel, these

clocks are enabled by the NADC and MADC clock dividers (page 0 / register 18, bit D7 = 1 and page 0 /

register 19, bit D7 = 1). When the ADC channel is powered down, the device internally initiates a

power-down sequence for proper shutdown. During this shutdown sequence, the NADC and MADC

dividers must not be powered down, or else a proper low-power shutdown may not take place. The user

can read back the power-status flag from page 0 / register 36, bit D6. When this flag indicates

power-down, the MADC divider may be powered down, followed by NADC divider.

When ADC_CLK (ADC processing clock) is derived from the NDAC divider output, the NDAC must be

kept powered up until the power-down status flags for ADC do not indicate power down. When the input to

the AOSR clock divider is derived from DAC_MOD_CLK, then MDAC must be powered up when ADC_fS

is needed (i.e., when WCLK is generated by TLV320AIC3110 or AGC is enabled) and can be powered

down only after the ADC power-down flags indicate power-down status.

In general, all the root clock dividers should be powered down only after the child clock dividers have been

powered down for proper operation.

The TLV320AIC3110 also has options for routing some of the internal clocks to the output pins of the

device to be used as general-purpose clocks in the system. The feature is shown in Figure 5-37.

Copyright 2009, Texas Instruments Incorporated

APPLICATION INFORMATION

67

Product Folder Link(s): TLV320AIC3110

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC3111IRHBT | AUDIO AMPLIFIER, PQCC32 |

| TLV320AIC3111IRHBR | AUDIO AMPLIFIER, PQCC32 |

| TLV320AIC3120IRHBR | AUDIO AMPLIFIER, PQCC32 |

| TLV320AIC3120IRHBT | AUDIO AMPLIFIER, PQCC32 |

| TLV320AIC31IRHBRG4 | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC3111 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Low-Power Audio Codec With Embedded miniDSP and Stereo Class-D Speaker Amplifier |

| TLV320AIC3111_101 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Low-Power Audio Codec With Embedded miniDSP and Stereo Class-D Speaker Amplifier |

| TLV320AIC3111EVM-K | 功能描述:音頻 IC 開發(fā)工具 TLV320AIC3111 Eval Mod RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| TLV320AIC3111IRHBR | 功能描述:接口—CODEC Low-Pwr Audio CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC3111IRHBT | 功能描述:接口—CODEC Low-Pwr Audio CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。