- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371180 > T8538B T8538B Quad Programmable Codec PDF資料下載

參數(shù)資料

| 型號: | T8538B |

| 元件分類: | Codec |

| 英文描述: | T8538B Quad Programmable Codec |

| 中文描述: | T8538B四可編程編解碼器 |

| 文件頁數(shù): | 33/44頁 |

| 文件大?。?/td> | 847K |

| 代理商: | T8538B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

Agere Systems Inc.

33

Preliminary Data Sheet

August 2001

T8538B Quad Programmable Codec

Timing Characteristics

(continued)

PCM Interface Timing

Single-Clocking Mode

Frame sync (FS) signifies the start of frame on the

PCM bus for all four channels. FS occurs every

125

μ

s at an 8 kHz rate. FS must be synchronous

with the PCM bus clock (BCLK) and must be high for a

minimum of one BCLK period. The PCM interface oper-

ates using fixed data rate timing, data timing for both

transmit and receive are controlled by BCLK. BCLK

can be any value from 512 kHz (eight time slots) to

16.384 MHz (256 time slots) as defined by Table 14.

The PCM bus transfers the most significant bit of the

time slot first, consistent with normal telephony prac-

tices. Figure 19 shows FS, transmit data (DX), and

receive data (DR) beginning on the rising edge of

BCLK and being latched on the falling edge of BCLK.

Figure 20 shows DX and DR beginning and FS being

latched on the rising edge of BCLK and DX and DR

being latched on the falling edge of BCLK.

Figure 19 portrays a bit offset of zero, and Figure 20

portrays a transmit bit offset of one and a receive bit

offset of two. Bit offset skews the PCM transmit and/or

receive data independently from the FS reference. Up

to seven BCLK cycles of bit offset can be employed on

a per-channel basis. This flexibility can accommodate

special timing requirements.

Linear coding is transmitted and received in two con-

secutive 8-bit time slots. TSX0 or TSX1 is active (low)

when DX data is transmitting (8 bits for companded

code, 16 bits for linear code).

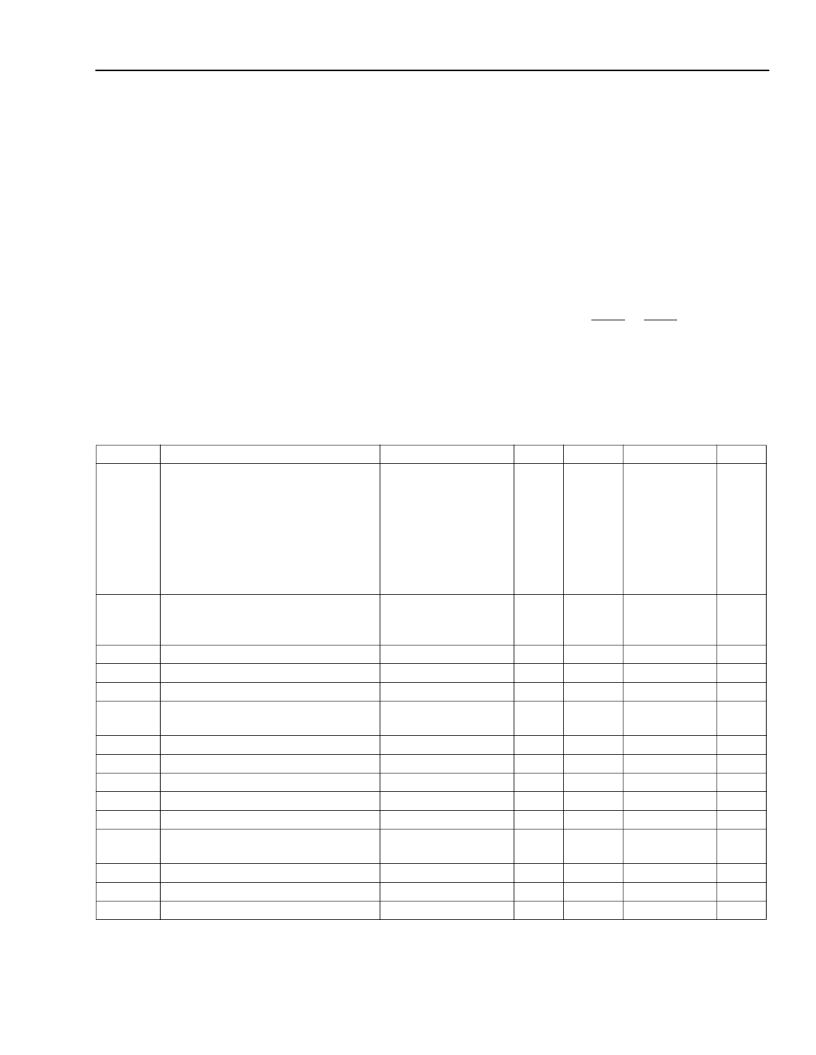

Table 14.

PCM Interface

Timing: Single-Clocking Mode

(See Figures 22 and 23.)

Symbol

f

BCLK

Parameter

Test Conditions

—

—

—

—

—

—

—

—

—

Min

—

—

—

—

—

—

—

—

—

Typ

512

1024

1536

2048

3072

4096

8192

16384

—

Max

—

—

—

—

—

—

—

—

Unit

kHz

kHz

kHz

kHz

kHz

kHz

kHz

kHz

—

Allowable BCLK Frequencies

—

Jitter of BCLK

100 ns in

100 ms =

1 ppm

60

—

—

125

μ

s

t

BCLK

—

BCLK Duty Cycle

Frame Strobe Setup Time

Frame Strobe Hold Time

Frame Strobe Width

—

40

7

4

t

BCLK

50

—

—

—

%

ns

ns

—

t

FSSETUP

t

FSHOLD

t

FSWIDTH

B

CLK

= 16.384 MHz

B

CLK

= 16.384 MHz

FS synchronous with

BCLK

B

CLK

= 16.384 MHz

B

CLK

= 16.384 MHz

B

CLK

= 16.384 MHz

B

CLK

= 16.384 MHz

B

CLK

= 16.384 MHz

I

L

= 15 mA,

C

LOAD

= 100 pF

C

LOAD

= 0

—

—

t

XDLY

t

IDHOLD

t

IDSETUP

t

RISE

t

FALL

t

RISE

,

t

FALL

t

DXHIGHZ

t

TSXDELAY

Line Driver Enable Delay

t

TSXHIGHZ

Line Driver Enable Float on TS Exit

Output Data Delay

Input Data Hold Time

Input Data Setup Time

Clock Edge Rise Time

Clock Edge Fall Time

DX Output Rise/Fall Time

—

4

7

—

—

—

—

—

—

—

—

—

9

—

—

8

8

30

ns

ns

ns

ns

ns

ns

DX Output Data Float on TS Exit

—

—

—

—

—

—

5

5

5

ns

ns

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T923CFAA | T92-Type 10 Gbits/s 1300 nm Uncooled DFB Laser Transmitter |

| T923WFAA | T92-Type 10 Gbits/s 1300 nm Uncooled DFB Laser Transmitter |

| T923FFAA | T92-Type 10 Gbits/s 1300 nm Uncooled DFB Laser Transmitter |

| TBA120T | FM IF amplifier and demodulator |

| TBA120 | Sound I.F. amplifier/demodulator for TV |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T85471G | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T85471J | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T8550VBAAA | 制造商:Arcolectric 功能描述:2 Pole Miniature rocker switch(Curved) 制造商:Arcolectric 功能描述:Double Pole,Miniature rocker switch(Curved),Standard Body with Terminal Barrier |

| T8553VBNAK | 制造商:Arcolectric 功能描述:Double Pole,Miniature rocker switch(Curved lit),Standard Body with Terminal Barrier 制造商:Arcolectric 功能描述:2 Pole Mini rocker switch(Curved lit) |

| T85751B | 制造商:ITF 制造商全稱:ITF 功能描述:857.5 MHz SAW Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復。