- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383876 > T7290A (Lineage Power) DS1/T1/CEPT/E1 Line Interface(DS1/T1/CEPT/E1 線接口) PDF資料下載

參數(shù)資料

| 型號(hào): | T7290A |

| 廠商: | Lineage Power |

| 英文描述: | DS1/T1/CEPT/E1 Line Interface(DS1/T1/CEPT/E1 線接口) |

| 中文描述: | DS1/T1/CEPT/E1線路接口(DS1/T1/CEPT/E1線接口) |

| 文件頁(yè)數(shù): | 6/24頁(yè) |

| 文件大小: | 420K |

| 代理商: | T7290A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

Data Sheet

April 1998

T7290A DS1/T1/CEPT/E1 Line Interface

6

Lucent Technologies Inc.

Receiver

Data Interface

The receive line-interface transmission format of the

T7290A device is alternate mark inversion (AMI). The

receive digital output format is dual-rail, nonreturn to

zero (NRZ). Receiver specifications are shown in

Table 2.

Clock Recovery and Data Retiming

The bipolar input signals from T1 and R1 are peak-

detected and sliced by the receiver front end. Timing

recovery is performed by a phase-locked loop (PLL)

that locks an internal free-running, current-controlled

oscillator (ICO) to the data-rate component. EC1, EC2,

and EC3 rate control inputs must be set appropriately

for DS1 or CEPT/E1 operation.

Frequency-Acquisition Aide

For robust operation, PLL is enhanced with a fre-

quency-acquisition capability. The frequency-acquisi-

tion circuitry is intended to guarantee proper phase

locking during start-up situations, such as powerup or

data activation. Once the T7290A device is phase-

locked to data, the frequency-acquisition mode is

not

activated unless a digital loss of signal occurs, in which

case RCLK is frequency-locked/phase-locked to

EXCLK. RCLK is always active and does not have any

instantaneous phase hits or discontinuities.

A continuously active (i.e., ungapped and unswitched)

reference clock must be present at EXCLK to enable

the frequency-acquisition circuitry. EXCLK must be an

independent reference such as an oscillator or system

clock for proper operation. The EXCLK clock frequency

must be 1.544 MHz

±

130 ppm for T1/DS1 operation or

2.048 MHz

±

80 ppm for CEPT/E1 operation.

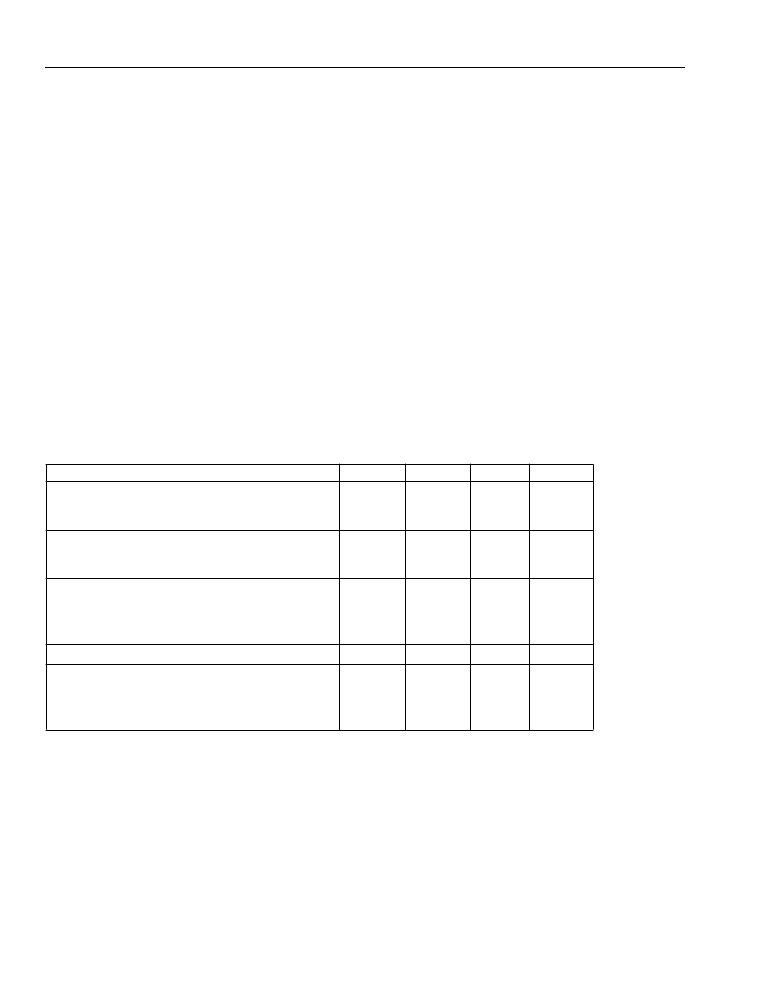

Table 2. Receiver Specifications

* Values shown are for flat loss only. Receiver also meets ITU-T G.703 interface immunity test (6 dB cable loss with

–18 dB interference) for CEPT/E1 operation.

Transfer characteristics (1/8 input).

The maximum number of consecutive zeros = 15.

§ Return loss specifications according to ITU-T G.703/RC6367A (CEPT only).

Parameter

Min

Typ

Max

Unit

Vp

Vp

Vp

Vp

Receiver Sensitivity:*

DS1

CEPT

Analog LOS Level:

DS1

CEPT

PLL:

3 dB Bandwidth

Peaking

ICO Free-run Frequency Error

Input Density (1s)

Return Loss:

§

51 kHz—102 kHz

102 kHz—2.048 MHz

2.048 MHz—3.072 MHz

0.85

0.7

—

—

—

—

—

—

0.48

0.28

—

—

—

—

—

12.5

33

1.2

—

—

—

2

±

6

—

kHz

dB

%

%

12

18

14

—

—

—

—

—

—

dB

dB

dB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7295-1 | E3 Integrated Line Receiver(E3 集成線接收器) |

| T7295-6 | DS3/SONET STS-1 Integrated Line Receiver(DS3/SONET STS-1 集成線接收器) |

| T7296 | Integrated Line Transmitter(集成PCM線傳送器) |

| T7502 | Dual PCM Codec with Filters(帶濾波器的雙PCM編解碼器) |

| T7503 | Dual PCM Codec with Filters(帶濾波器的雙PCM編解碼器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T-7290A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:T7290A DS1/T1/CEPT Line Interface |

| T-7290A-EL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:T7290A DS1/T1/CEPT Line Interface |

| T-7290A--EL | 制造商:Alcatel-Lucent 功能描述:DATACOM, PCM TRANSCEIVER, PDSO28 |

| T7290A-EL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:T7290A DS1/T1/CEPT Line Interface |

| T-7290A--EL-DT | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。