- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98146 > ST7260E2M1/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | ST7260E2M1/XXX |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 |

| 封裝: | 0.300 INCH, LEAD FREE, PLASTIC, SOP-24 |

| 文件頁數(shù): | 68/118頁 |

| 文件大小: | 2304K |

| 代理商: | ST7260E2M1/XXX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁當前第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

ST7260

53/117

16-BIT TIMER (Cont’d)

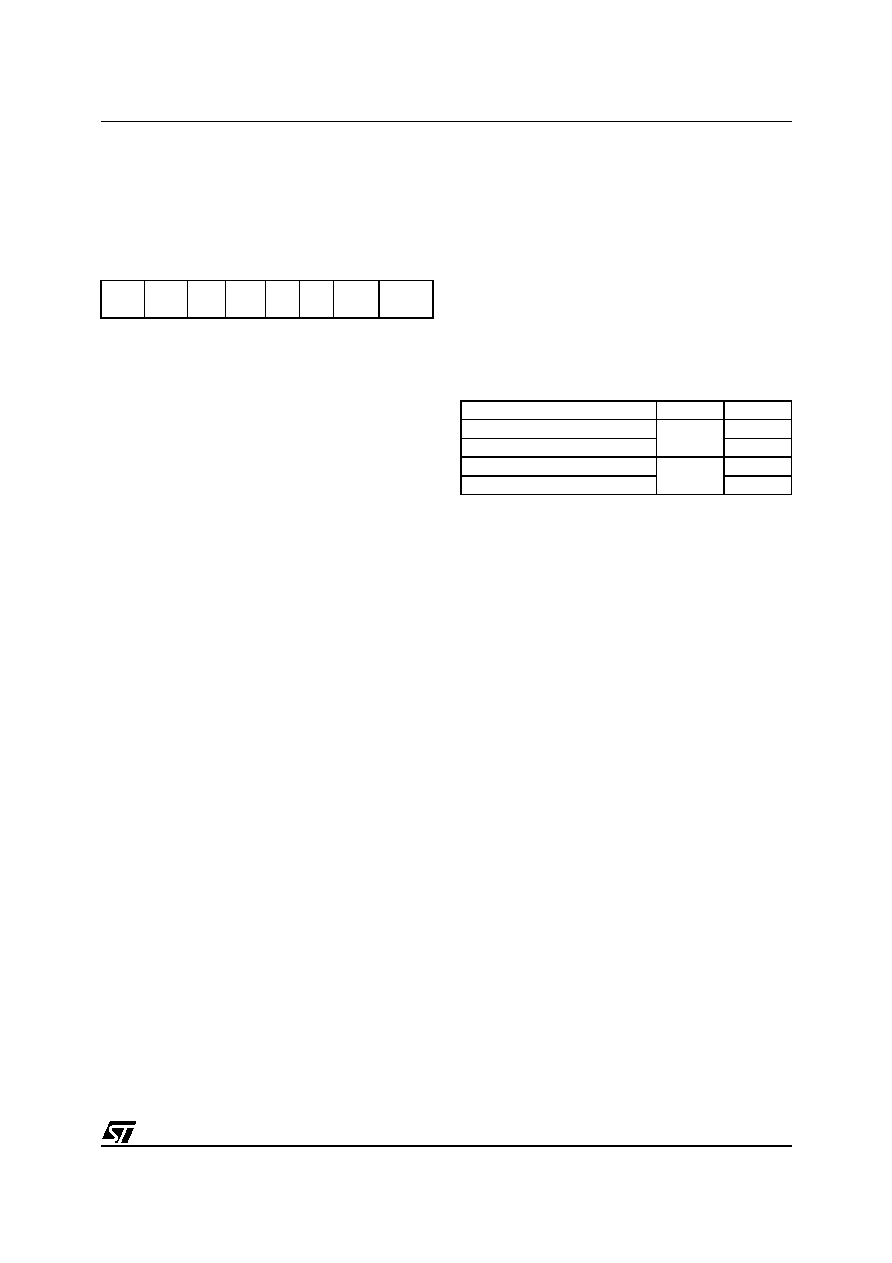

CONTROL REGISTER 2 (CR2)

Read/Write

Reset Value: 0000 0000 (00h)

Bit 7 = OC1E Output Compare 1 Pin Enable.

This bit is used only to output the signal from the

timer on the OCMP1 pin (OLV1 in Output Com-

pare mode, both OLV1 and OLV2 in PWM and

one-pulse mode). Whatever the value of the OC1E

bit, the Output Compare 1 function of the timer re-

mains active.

0: OCMP1 pin alternate function disabled (I/O pin

free for general-purpose I/O).

1: OCMP1 pin alternate function enabled.

Bit 6 = OC2E Output Compare 2 Pin Enable.

This bit is used only to output the signal from the

timer on the OCMP2 pin (OLV2 in Output Com-

pare mode). Whatever the value of the OC2E bit,

the Output Compare 2 function of the timer re-

mains active.

0: OCMP2 pin alternate function disabled (I/O pin

free for general-purpose I/O).

1: OCMP2 pin alternate function enabled.

Bit 5 = OPM One Pulse Mode.

0: One Pulse mode is not active.

1: One Pulse mode is active, the ICAP1 pin can be

used to trigger one pulse on the OCMP1 pin; the

active transition is given by the IEDG1 bit. The

length of the generated pulse depends on the

contents of the OC1R register.

Bit 4 = PWM Pulse Width Modulation.

0: PWM mode is not active.

1: PWM mode is active, the OCMP1 pin outputs a

programmable cyclic signal; the length of the

pulse depends on the value of OC1R register;

the period depends on the value of OC2R regis-

ter.

Bit 3, 2 = CC[1:0] Clock Control.

The timer clock mode depends on these bits:

Table 17. Clock Control Bits

Note: If the external clock pin is not available, pro-

gramming the external clock configuration stops

the counter.

Bit 1 = IEDG2 Input Edge 2.

This bit determines which type of level transition

on the ICAP2 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

Bit 0 = EXEDG External Clock Edge.

This bit determines which type of level transition

on the external clock pin EXTCLK will trigger the

counter register.

0: A falling edge triggers the counter register.

1: A rising edge triggers the counter register.

70

OC1E OC2E OPM PWM CC1 CC0 IEDG2 EXEDG

Timer Clock

CC1

CC0

fCPU / 4

0

fCPU / 2

1

fCPU / 8

1

0

External Clock (where available)

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST72T141K2M6XXX | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| ST72T141K2M3XXX | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| ST72T141K2MARE | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| ST7FL09Y0MATRE | 8-BIT, FLASH, 16 MHz, MICROCONTROLLER, PDSO16 |

| ST7FL09Y0MBE | 8-BIT, FLASH, 16 MHz, MICROCONTROLLER, PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST72611F1 | 制造商:STMicroelectronics 功能描述:LOW SPEED USB 8-BIT MCU WITH 3 ENDPOINTS,FLASH MEMORY, - Bulk |

| ST7263-EMU2 | 功能描述:仿真器/模擬器 ST7 Emulator Board RoHS:否 制造商:Blackhawk 產(chǎn)品:System Trace Emulators 工具用于評估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| ST7265X-EVAL/MS | 制造商:STMicroelectronics 功能描述:ST6 EVAL BD - Bulk |

| ST7265X-EVAL/PFD | 制造商:STMicroelectronics 功能描述:USB FLASH EVAL - Bulk |

| ST7266 | 制造商:6940 功能描述:ST7266 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。