- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98143 > ST16C654IQ64/TR (EXAR CORP) 4 CHANNEL(S), 1.5M bps, SERIAL COMM CONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | ST16C654IQ64/TR |

| 廠商: | EXAR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4 CHANNEL(S), 1.5M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, LQFP-64 |

| 文件頁數(shù): | 11/54頁 |

| 文件大?。?/td> | 734K |

| 代理商: | ST16C654IQ64/TR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

ST16C654/654D

xr

2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO

REV. 5.0.2

16

2.11

Auto RTS Hardware Flow Control

Automatic RTS hardware flow control is used to prevent data overrun to the local receiver FIFO. The RTS#

output is used to request remote unit to suspend/resume data transmission. The auto RTS flow control

features is enabled to fit specific application requirement (see Figure 11):

Enable auto RTS flow control using EFR bit-6.

The auto RTS function must be started by asserting RTS# output pin (MCR bit-1 to logic 1 after it is enabled).

If needed, the RTS interrupt can be enabled through IER bit-6 (after setting EFR bit-4). The UART issues an

interrupt when the RTS# pin makes a transition from low to high: ISR bit-5 will be set to logic 1.

2.12

Auto CTS Flow Control

Automatic CTS flow control is used to prevent data overrun to the remote receiver FIFO. The CTS# input is

monitored to suspend/restart the local transmitter. The auto CTS flow control feature is selected to fit specific

application requirement (see Figure 11):

Enable auto CTS flow control using EFR bit-7.

If needed, the CTS interrupt can be enabled through IER bit-7 (after setting EFR bit-4). The UART issues an

interrupt when the CTS# pin is de-asserted (logic 1): ISR bit-5 will be set to 1, and UART will suspend

transmission as soon as the stop bit of the character in process is shifted out. Transmission is resumed after

the CTS# input is re-asserted (logic 0), indicating more data may be sent.

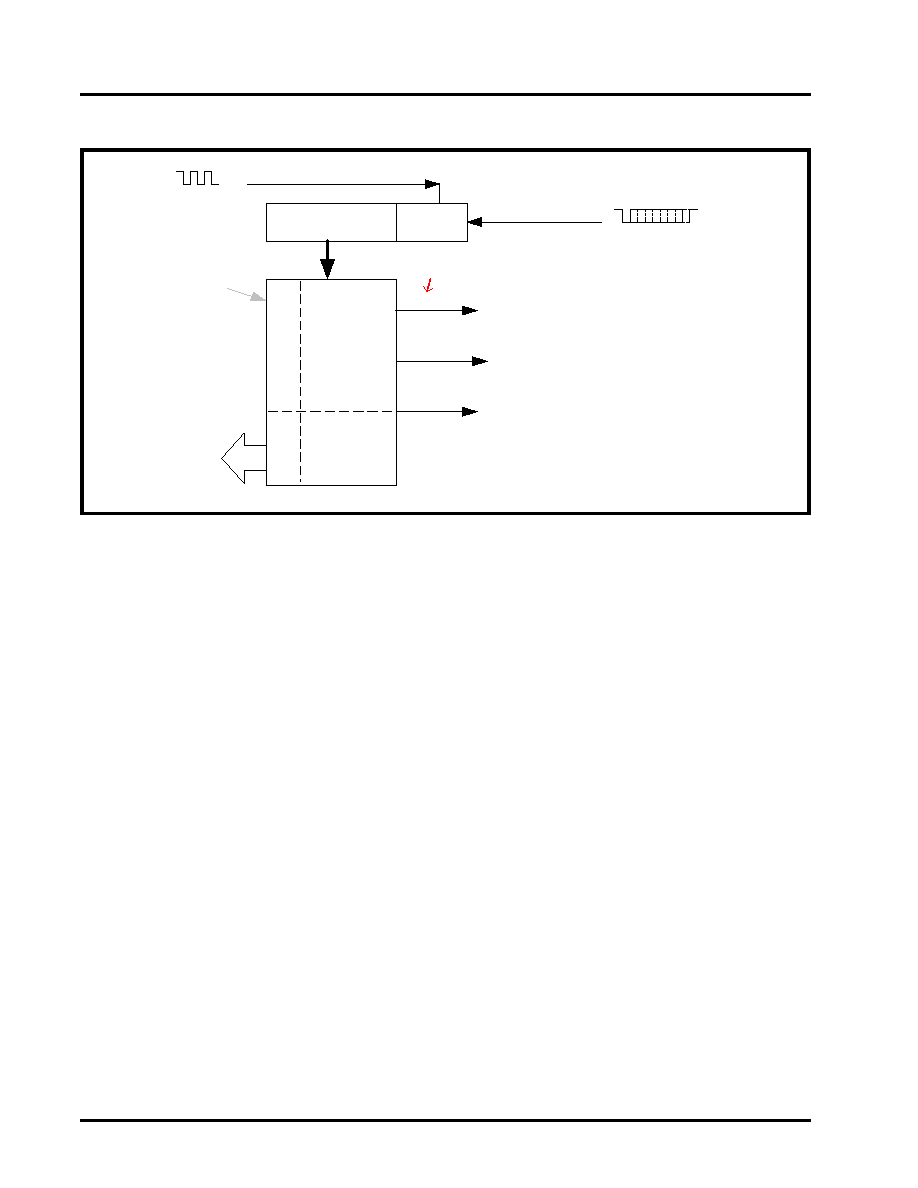

FIGURE 10. RECEIVER OPERATION IN FIFO AND AUTO RTS FLOW CONTROL MODE

Receive Data Shift

Register (RSR)

RXFIFO1

16X Clock

E

rror

T

ags

(64-

sets)

E

rro

rTa

gs

in

LSR

b

its

4

:2

64 bytes by 11-bit

wide

FIFO

Receive Data Characters

FIFO

Trigger=16

Example

:

- RX FIFO trigger level selected at 16 bytes

Data fills to

56

Data falls to

8

Data Bit

Validation

Receive

Data FIFO

Receive

Data

Receive Data

Byte and Errors

RHR Interrupt (ISR bit-2) programmed for

desired FIFO trigger level.

FIFO is Enabled by FCR bit-0=1

RTS# de-asserts when data fills above the flow

control trigger level to suspend remote transmitter.

Enable by EFR bit-6=1, MCR bit-1.

RTS# re-asserts when data falls below the flow

control trigger level to restart remote transmitter.

Enable by EFR bit-6=1, MCR bit-1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST18931CR | 16-BIT, 50 MHz, OTHER DSP, CPGA121 |

| ST40RA150XH6 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA372 |

| ST40RA200XH6E | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA372 |

| ST52510F3M6 | MICROCONTROLLER, PDSO20 |

| ST52E430B/D | 8-BIT, UVPROM, 20 MHz, MICROCONTROLLER, CDIP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST16C654IQ64TR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 3.3V/5V 64-Pin LQFP T/R 制造商:Exar Corporation 功能描述:ST16C654IQ64TR-F |

| ST16CF54 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Smartcard MCU With 4 KBytes EEPROM 512 Bits Modular Arithmetic Processor |

| ST16CQ32245TBR | 功能描述:開關(guān) IC - 各種 Advanced Logic Signal Switch RoHS:否 制造商:Fairchild Semiconductor 開啟電阻(最大值): 電源電壓-最大:4.4 V 電源電壓-最小:2.5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:WLCSP-9 封裝:Reel |

| ST16DD00 | 功能描述:撥動開關(guān) TOGGLE RoHS:否 制造商:C&K Components 觸點形式:DPDT 開關(guān)功能:ON - ON - ON 電流額定值: 電壓額定值 AC:20 V 電壓額定值 DC:20 V 功率額定值:0.4 VA 端接類型:V-Bracket 安裝風(fēng)格: 端子密封:Epoxy 觸點電鍍:Gold 照明:Not Illuminated |

| ST16FJ | 制造商:Panasonic Electric Works 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。