- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98142 > SST89V516RD-33-I-PIE 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 PDF資料下載

參數(shù)資料

| 型號: | SST89V516RD-33-I-PIE |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 |

| 封裝: | LEAD FREE, PLASTIC, MS-011AC, DIP-40 |

| 文件頁數(shù): | 32/80頁 |

| 文件大小: | 934K |

| 代理商: | SST89V516RD-33-I-PIE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

38

Data Sheet

FlashFlex51 MCU

SST89E516RD2 / SST89E516RD

SST89V516RD2 / SST89V516RD

2005 Silicon Storage Technology, Inc.

S71273-01-000

3/05

There are no IAP counterparts for the external host com-

mands Select-Block0 and Select-Block1.

4.2.5 Polling

A command that uses the polling method to detect flash

operation completion should poll on the FLASH_BUSY bit

(SFST[2]). When FLASH_BUSY de-asserts (logic 0), the

device is ready for the next operation.

MOVC instruction may also be used for verification of the

Programming and Erase operation of the flash memory.

MOVC instruction will fail if it is directed at a flash block that

is still busy.

4.2.6 Interrupt Termination

If interrupt termination is selected, (SFCM[7] is set), then

an interrupt (INT1) will be generated to indicate flash opera-

tion completion. Under this condition, the INT1 becomes an

internal interrupt source. The INT1# pin can now be used

as a general purpose port pin and it cannot be the source

of External Interrupt 1 during in-application programming.

In order to use an interrupt to signal flash operation termi-

nation. EX1 and EA bits of IE register must be set. The IT1

bit of TCON register must also be set for edge trigger

detection.

.

Note: DISIAPL pin in PLCC or TQFP will also disable IAP commands if it is externally pulled low when reset.

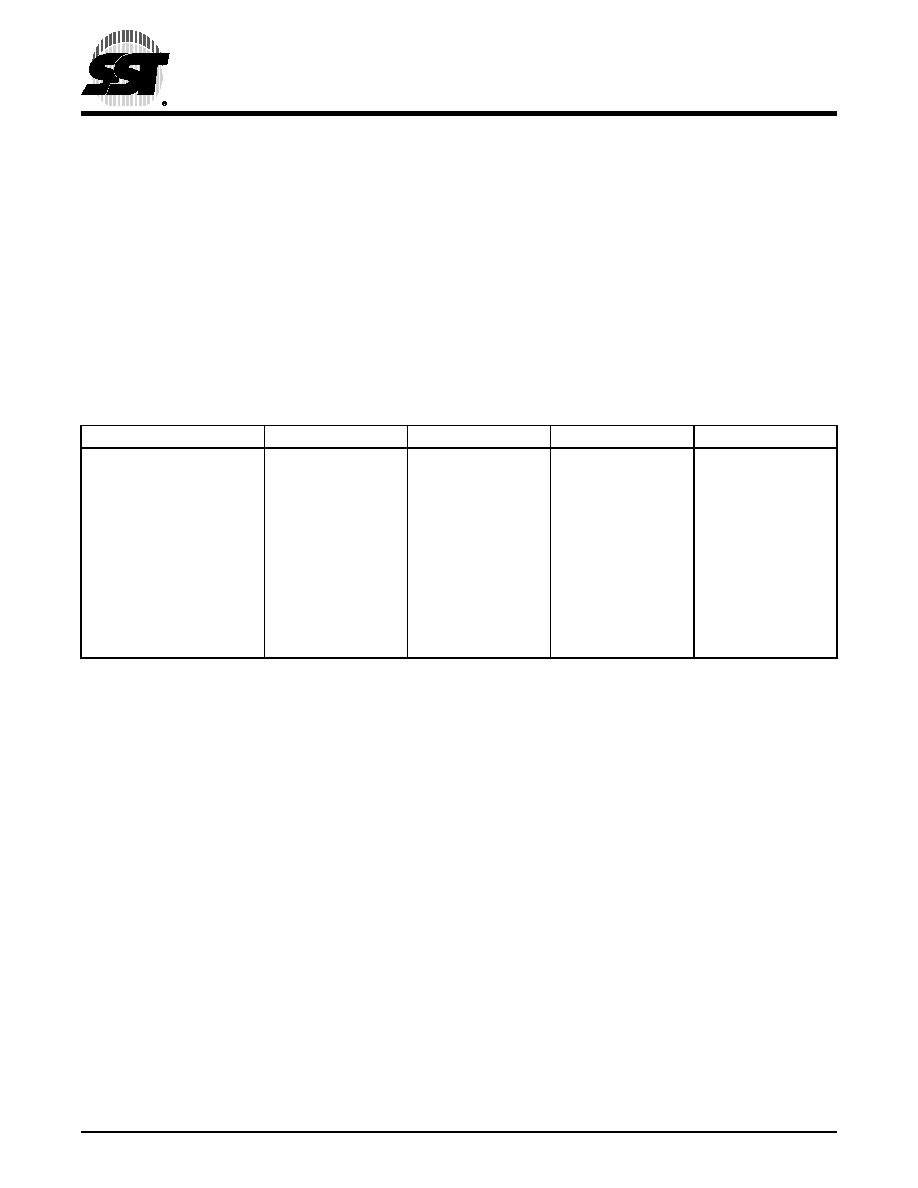

TABLE

4-3: IAP COMMANDS1

1. SFCF[6]=1 enables IAP commands; SFCF[6]=0 disables IAP commands.

Operation

SFCM [6:0]2

2. Interrupt/Polling enable for flash operation completion

SFCM[7] = 1: Interrupt enable for flash operation completion

0: polling enable for flash operation completion

SFDT [7:0]

SFAH [7:0]

SFAL [7:0]

Chip-Erase3

3. Chip-Erase only functions in IAP mode when EA#=0 (external memory execution) and device is not in level 4 locking.

01H

55H

X4

4. X can be VIL or VIH, but no other value.

X

Block-Erase5

5. Refer to Table 4-2 for address resolution

0DH

55H

AH

X

Sector-Erase5

0BH

X

AH6

6. AH = Address high order byte

AL7

7. AL = Address low order byte

Byte-Program5

0EH

DI8

8. DI = Data Input, DO = Data Output, all other values are in hex.

AH

AL

Byte-Verify (Read)5

0CH

DO8

AH

AL

Prog-SB19

9. Instruction must be located in Block 1 or external code memory.

0FH

AAH

X

03H

AAH

X

05H

AAH

X

09H

AAH

5AH

X

Enable-Clock-Double9

08H

AAH

55H

X

T4-3.0 1273

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SST89V516RD-33-C-PI | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 |

| SST89V516RD-33-I-PIE | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 |

| SST89E516RD-40-I-PIE | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PDIP40 |

| SST89V554A-33-C-TQJ | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PQFP44 |

| SST89E554A-40-C-NJ | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SST89V516RD-33-I-QIF | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex MCU |

| SST89V52RD2 | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89V52RD2/RD | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89V52RD2-33-C-NI | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89V52RD2-33-C-NIE1 | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。