- 您現在的位置:買賣IC網 > PDF目錄374749 > SDA9251-2X (SIEMENS A G) 868352-Bit Dynamic Sequential Access Memory for Television Applications (TV-SAM) PDF資料下載

參數資料

| 型號: | SDA9251-2X |

| 廠商: | SIEMENS A G |

| 元件分類: | DRAM |

| 英文描述: | 868352-Bit Dynamic Sequential Access Memory for Television Applications (TV-SAM) |

| 中文描述: | 212K X 4 VIDEO DRAM, 25 ns, PDSO28 |

| 文件頁數: | 3/23頁 |

| 文件大小: | 771K |

| 代理商: | SDA9251-2X |

SDA 9251-2X

Semiconductor Group

161

Data Input (SDC, SCB)

Data are shifted in through the serial port C (SDC0, …, SDC3) at the rising edge of the shift clock

SCB. After16 clock pulses the data have to be transferred from shift register C to latch C. If more

than 16 clock pulses occur before latching the data, only the last sixteen 4-bit data values are

accepted.

Data Transfer from Shift Register C to Latch C (WT)

The contents of the shift register C are transferred to latch C at the falling edge of the write transfer

signal WT. If the timing restrictions between WT and the clock SCB are respected, a continuous

data flow at input SDC is possible without loosing data. This transfer operation may be

asynchronous to all other transfer operations except for a small forbidden window conditioned by

the latch C to memory transfer,

see diagram 4

.

Write Transfer from Latch C to Memory (RE)

The data of latch C are transferred to the preaddressed location of the memory array at the rising

edge of RE, if the mode bits were set to H (M1) and L (M0), see “Addressing and Mode Control.”

Addressing and Mode Control (SAR, SAC, SCAD, RE)

The serial 8-bit row address SAR and the 8-bit column address/mode code SAC are serially shifted

into the TV-SAM (LSB first) at rising edge of the address clock SCAD. After 8 SCAD cycles, the

falling edge of RE internally latches SAR and SAC. The column address itself needs only 6 bits. The

last 2 bits of SAC are defined as mode bits and determine the read/write and refresh operation of

the memory arrays to be triggered by the RE signal.

Read Transfer from Memory to Latch A or B (RE)

Memory data from a preaddressed location are transferred to latch A or B at the falling edge of RE,

depending on the mode control bits, see “Addressing and Mode Control”.

Data Transfer from Latch A to Shift Register A (RA)

The contents of latch A are transferred to shift register A at the falling edge of the read transfer

signal RA. If the timing restrictions between RA and the shift clock SCA are taken into account, a

continuous data flow at output SQA without interrupts is possible. This transfer operation is

independent on all other transfer operations except for a small forbidden time window conditioned

by the memory to latch A transfer.

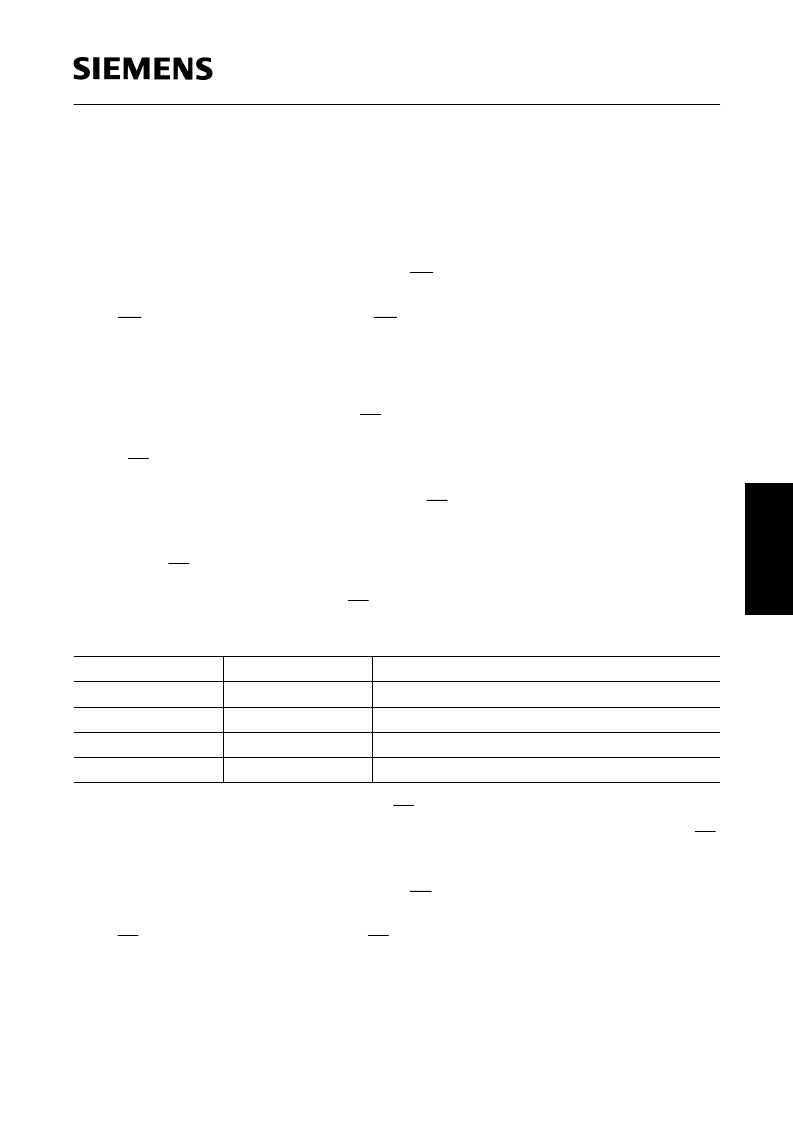

Mode Bit M1

Mode Bit M0

Operation

L

L

Read transfer from memory to latch A

L

H

Read transfer from memory to latch B

H

L

Write transfer from latch C to memory

H

H

Refresh with internal row address

相關PDF資料 |

PDF描述 |

|---|---|

| SDA9253 | 2.6 MBit Dynamic Sequential Access Memory for Television Applications (TV-SAM) |

| SDA9254-2 | 2.6 MBit Dynamic Sequential Access Memory for Television Applications (TV-SAM) with On-chip Noise Reduction Filter |

| SDA9257 | Clock Sync Generator |

| SDA9280 | ICs for Consumer Electronics |

| SDA9280B22 | ICs for Consumer Electronics |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SDA9253 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2.6 MBit Dynamic Sequential Access Memory for Television Applications (TV-SAM) |

| SDA9254-2 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2.6 MBit Dynamic Sequential Access Memory for Television Applications (TV-SAM) with On-chip Noise Reduction Filter |

| SDA9255 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:SRC-Scan Rate Converter SDA9255 |

| SDA9257 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:Clock Sync Generator |

| SDA9270 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:ICs for Consumer Electronics |

發(fā)布緊急采購,3分鐘左右您將得到回復。