- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368391 > PXASCC (NXP Semiconductors N.V.) CMOS 16-bit communications microcontroller(CMOS 16位通信微控制器) PDF資料下載

參數(shù)資料

| 型號: | PXASCC |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | CMOS 16-bit communications microcontroller(CMOS 16位通信微控制器) |

| 中文描述: | 的CMOS 16位微控制器通信的CMOS(16位通信微控制器) |

| 文件頁數(shù): | 30/42頁 |

| 文件大小: | 229K |

| 代理商: | PXASCC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary specification

XA-SCC

CMOS 16-bit communications microcontroller

1999 Mar 29

30

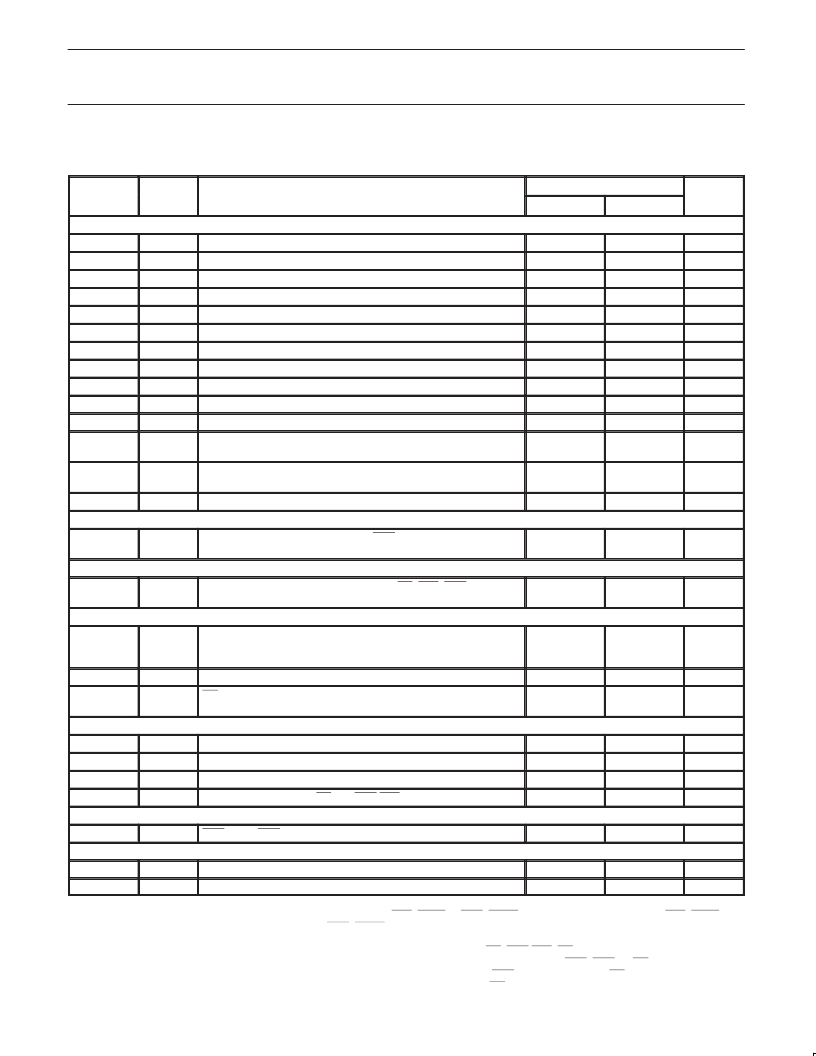

AC ELECTRICAL CHARACTERISTICS (3.3V

V

DD

= 3.3V

10%, T

amb

= –40 C to +85 C (industrial)

10%)

LIMITS

SYMBOL

FIGURE

PARAMETER

MIN

MAX

UNIT

All Cycles

F

C

25

System Clock (internally called CClk) Frequency

0

30

MHz

t

C

25

System Clock Period = 1/FC

33.33

–

ns

t

CHCX

t

CLCX

t

CLCH

t

CHCL

t

AVSL

t

CHAH

t

CHAV

t

CHSH

t

CHSL

t

CODH

25

XTALIN High Time

t

C

* 0.5

t

C

* 0.4

–

–

ns

25

XTALIN Low Time

–

ns

25

XTALIN Rise Time

5

ns

25

XTALIN Fall Time

–

5

ns

All

Address Valid to Strobe low

Address hold after CLKOUT rising edge

9

t

C

– 21

1

–

ns

All

–

ns

All

Delay from CLKOUT rising edge to address valid

Delay from CLKOUT rising edge to Strobe High

9

Delay from CLKOUT rising edge to Strobe Low

9

–

30

ns

All

1

28

ns

All

1

25

ns

26

ClkOut Duty Cycle High (into 40pF max.)

(See

Warning

Note 5 on page 31.)

t

CHCX

–7

t

CHCX

+3

ns

t

CPWH

13, 14, 16,

20, 21, 22

CAS Pulse Width High

t

C

– 12

–

ns

t

CPWL

13, 21

CAS Pulse Width Low

t

C

– 10

–

ns

All DRAM cycles

t

RP

24

RAS precharge time, thus minimum RAS high time

8

(n * t

C

) –16

note 8

–

ns

Generic Data Read Only

t

AHDR

9, 16

Address hold (A19–A1 only, not A0) after CS, BLE, BHE rise at end

of Generic Data Read Cycle (not code fetch)

t

C

–12

–

ns

Data Read and Instruction Fetch Cycles

t

DIS

9, 10,

12–14, 16,

17, 20, 21

Data In Valid setup to ClkOut rising edge

32

–

ns

t

DIH

t

OHDE

Data In Valid hold after ClkOut rising edge

2

0

–

ns

10, 12, 13,

16, 20, 21

OE high to XA Data Bus Driver Enable

t

C

– 19

–

ns

Write Cycles

t

CHDV

t

DVSL

t

SHAH

t

SHDH

Refresh

t

CLRL

Wait Input

t

WS

t

WH

NOTES:

1. On a 16 bit bus, if only one byte is being written, then only one of BLE_CASL or BHE_CASH will go active. On an 8 bit bus, BLE_CASL

goes active for all (odd or even address) accesses. BHE_CASH will not go active during any accesses on an 8 bit bus.

2. The bus timing is designed to make meeting hold time very straightforward without glue logic. On all generic reads and fetches, in order to

meet hold time, the slave device should hold data valid on the bus until the earliest of CS, BHE/BLE, OE, goes high (inactive), or until the

address changes. On all FPM DRAM reads and fetches, hold data valid on the bus until the earliest of RAS, CAS, or OE goes high

(inactive.) On all EDO DRAM reads and fetches, hold data valid on the bus until a new CAS is asserted, or until OE goes high (inactive.)

3. To avoid tri-state fights during read cycles and fetch cycles, do not drive data bus until OE goes active

Clock High to Data Valid

–

30

ns

Data Valid prior to Strobe Low

t

C

– 23

t

C

– 25

t

C

– 25

–

ns

11, 16

Minimum Address Hold Time after strobe goes inactive

–

ns

Data hold after strobes (CS and BHE/BLE) high

–

ns

21

CAS low to RAS low

t

C

– 15

–

ns

24

WAIT setup (stable high or low) prior to CLKOUT rising edge

25

–

ns

24

WAIT hold (stable high or low) after CLKOUT rising edge

0

–

ns

相關PDF資料 |

PDF描述 |

|---|---|

| PXASCCKFBE | CMOS 16-bit communications microcontroller |

| PXB9202 | ?Broadband Communication Controller |

| PXC2081 | 480CH 8bit TFT LCD Source Driver with mini-LVDS interface |

| PXC2081COF | 480CH 8bit TFT LCD Source Driver with mini-LVDS interface |

| PXC2081TCP | 480CH 8bit TFT LCD Source Driver with mini-LVDS interface |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PXASCCKFBE | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS 16-bit communications microcontroller |

| PXB 4210 EL V1.2-G | 制造商:Lantiq 功能描述:LTQPXB 4210 EL V1.2-G LQ000001141_GRX288 |

| PXB 4219 E V3.4 | 功能描述:IC ATM/IP INTERWORKING BGA-256 RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| PXB 4220 E V3.4-G | 功能描述:IC ATM/IP INTERWORKING BGA-256 RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| PXB 4221 E V3.4-G | 功能描述:IC ATM/IP INTERWORKING BGA-256 RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

發(fā)布緊急采購,3分鐘左右您將得到回復。