- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368020 > PI7C8150B PCI Bridge | Asynchronous 2-Port PCI Bridge PDF資料下載

參數(shù)資料

| 型號(hào): | PI7C8150B |

| 英文描述: | PCI Bridge | Asynchronous 2-Port PCI Bridge |

| 中文描述: | PCI橋|異步2端口PCI橋 |

| 文件頁(yè)數(shù): | 83/115頁(yè) |

| 文件大小: | 879K |

| 代理商: | PI7C8150B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)當(dāng)前第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)

PI7C8150B

2-PORT PCI-TO-PCI BRIDGE

ADVANCE INFORMATION

Page 83 of 115

July 31, 2003 – Revision 1.031

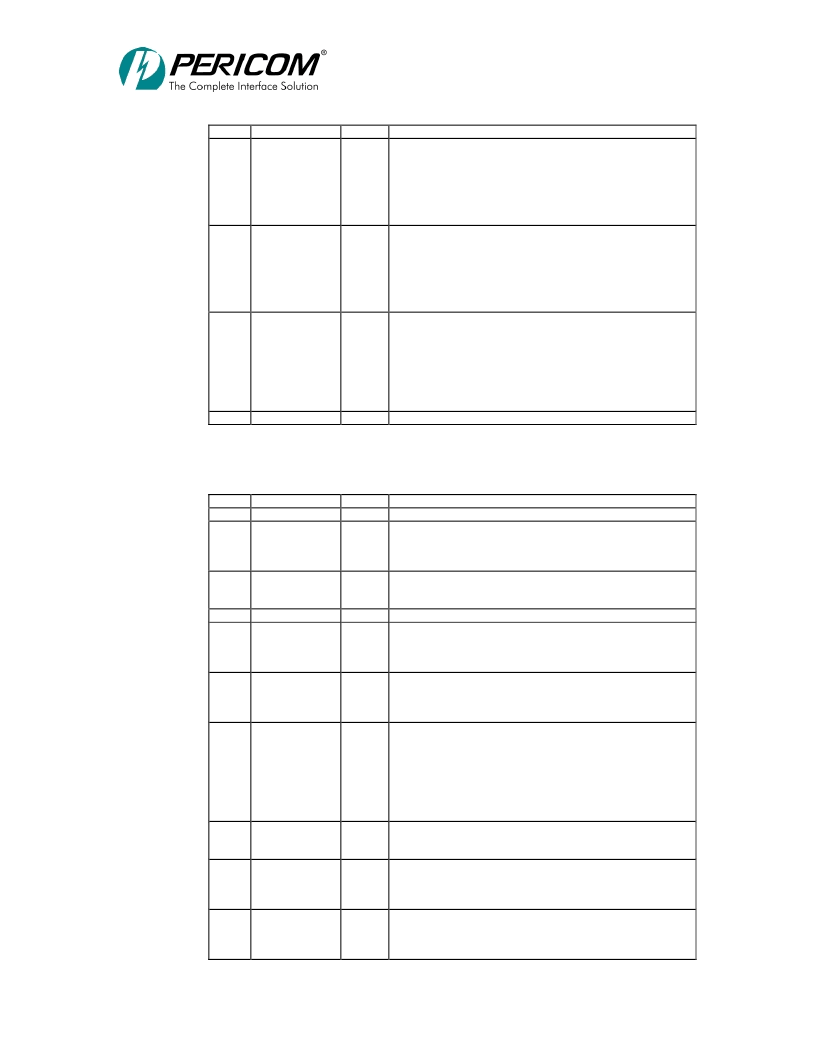

Bit

Function

Type

Description

Controls the ability to perform address / data stepping

0: disable address/data stepping (affects primary and secondary)

1: enable address/data stepping (affects primary and secondary)

Reset to 0

Controls the enable for the P_SERR_L pin

0: disable the P_SERR_L driver

1: enable the P_SERR_L driver

Reset to 0

Controls 7C8150’s ability to generate fast back-to-back transactions

to different devices on the primary interface.

0: no fast back-to-back transactions

1: enable fast back-to-back transactions

Reset to 0

Returns 000000 when read

7

Wait Cycle

Control

R/O

8

P_SERR_L

enable

R/W

9

Fast Back-to-

Back Enable

R/W

15:10

Reserved

R/O

14.1.4

STATUS REGISTER – OFFSET 04h

Bit

19:16

20

Function

Reserved

Capabilities List

Type

R/O

R/O

Description

Reset to 0

Set to 1 to enable support for the capability list (offset 34h is the

pointer to the data structure)

Reset to 1

Set to 1 to enable 66MHz operation on the primary interface

Reset to 1

Reset to 0

Set to 1 to enable decoding of fast back-to-back transactions on the

primary interface to different targets

Reset to 1

Set to 1 when P_PERR_L is asserted and bit 6 of command register

is set

Reset to 0

DEVSEL_L timing (medium decoding)

00: fast DEVSEL_L decoding

01: medium DEVSEL_L decoding

10: slow DEVSEL_L decoding

11: reserved

Reset to 01

Set to 1 (by a target device) whenever a target abort cycle occurs

Reset to 0

Set to 1 (by a master device) whenever transactions are terminated

with target aborts

Reset to 0

Set to 1 (by a master) when transactions are terminated with Master

Abort

Reset to 0

21

66MHz Capable

R/O

22

23

Reserved

Fast Back-to-

Back Capable

R/O

R/O

24

Data Parity Error

Detected

R/WC

26:25

DEVSEL_L

timing

R/O

27

Signaled Target

Abort

R/WC

28

Received Target

Abort

R/WC

29

Received Master

Abort

R/WC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C8152A | ENHANCED 2- PORT TO PCI BRIDGE INTEL 21152 COMPORISON |

| PI7C81552 | ENHANCED 2-PORT PCI TO PCI BRIDGE INTEL 21152 COMPARISON |

| PI7C81552A | ENHANCED 2-PORT PCI TO PCI BRIDGE INTEL 21152 COMPARISON |

| PI7C8152 | ENHANCED 2- PORT TO PCI BRIDGE INTEL 21152 COMPORISON |

| PI7C8154B | 2 PORT 64 BIT 66MHZ PCI TO PCI BRIDGE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C8150B-33 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | Asynchronous 2-Port PCI Bridge |

| PI7C8150BEVB | 功能描述:界面開發(fā)工具 2 Port PCI Bridge Eval Brd RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| PI7C8150BMA | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE |

| PI7C8150BMA-33 | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE |

| PI7C8150BMAE | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 32-Bit PCI Bridge 2 Port RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。