- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369949 > PCF8890 240 + 1 outputs TFT LCD gate driver PDF資料下載

參數(shù)資料

| 型號: | PCF8890 |

| 英文描述: | 240 + 1 outputs TFT LCD gate driver |

| 中文描述: | 240 1輸出TFT液晶柵極驅(qū)動器 |

| 文件頁數(shù): | 54/76頁 |

| 文件大小: | 385K |

| 代理商: | PCF8890 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當(dāng)前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

2002 Aug 16

54

Philips Semiconductors

Preliminary specification

STN RGB - 384 output column driver

PCF8832

Notes

1.

All timing values are valid within the operating ambient temperature and supply voltage ranges and are referred to

V

IL

and V

IH

with an input voltage swing of V

SS1

to V

DD1

.

Not directly observable at any pin.

C

b

= total capacitance of one bus line in pF.

The input signal rise time and fall time (t

r

and t

f

) are specified at 15 ns or less. When the cycle time is used at

high-speed, the specification is t

r

+ t

f

≤

(T

CYC

t

CCLW

t

CCHW

) or t

r

+ t

f

≤

(T

CYC

t

CCLR

t

CCHR

).

The system cycle time can be derated for different values of V

DD1

. For V

DD1

< 2.5 V the system cycle time can be

calculated as follows:

at V

DD1

= 2.5 V, f

CYC(2.5)

= 6.25 MHz and

f = 0.44 MHz/V then

The input signal rise time and fall time (t

r

and t

f

) are specified at 15 ns or less. When the cycle time is used at

high-speed, the specification is t

r

+ t

f

≤

(T

CYC

t

EH

t

EL

).

The input signal rise time and fall time (t

r

and t

f

) are specified at 15 ns or less.

2.

3.

4.

5.

MHz.

6.

7.

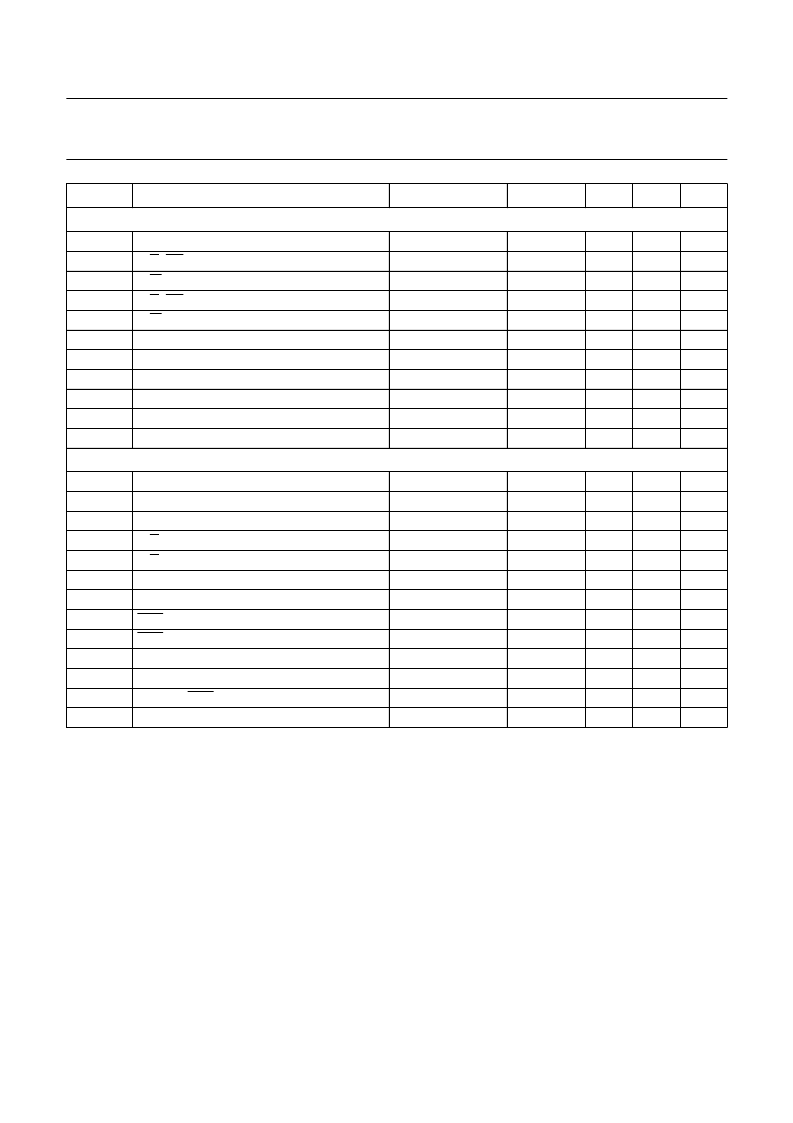

8-bit parallel (6800-type) interface

; note 6; see Fig.57

T

CYC

t

AS1

t

AS2

t

AH1

t

AH2

t

DS

t

DH

t

OH

t

ACC

t

EH

t

EL

Serial interface

; note 7; see Figs 58

,

59 and 60

system cycle time

D/C, CS address set-up time

R/W address set-up time

D/C, CS address hold time

R/W address hold time

D0 to D7 data set-up time

D0 to D7 data hold time

D0 to D7 output disable time

D0 to D7 access time

E pulse width HIGH

E pulse width LOW

160

50

50

10

35

20

10

10

40

60

30

70

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

C

L

= 50 pF

T

SCYC

t

SHW

t

SLW

t

SAH

t

SAS

t

SDS

t

SDH

t

CSS

t

CSH

t

ODE1

t

ODE2

t

CEH

t

ACC

serial clock SCLK period

SCLK pulse width HIGH

SCLK pulse width LOW

D/C address hold time

D/C address setup time

SDI data set-up time

SDI data hold time

SCE to SCLK set-up time

SCE to SCLK hold time

SDO disable time

SDO disable time

SCLK to SCE hold time

SCLK to SDO access time

160

60

60

70

45

45

50

30

120

25

50

50

100

50

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

f

CYC(VDD1)

f

CYC(2.5)

0.44

V

DD1

×

×

=

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF93C110 | 32-Bit Microcontroller |

| PCB93C110 | 32-Bit Microcontroller |

| PCG3N60C3W | TRANSISTOR | IGBT | N-CHAN | 600V V(BR)CES | CHIP |

| PCG4AX280MM | FUEHRUNGSSCHIENE LEITERPLATTE 280MM |

| PCH-1415FN | CLIP PIPE 15MM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-CF8GB-266W-DVDC | 制造商:PNY Technologies 功能描述:OPTIMA PRO UDMA 8GB CF CARD - Bulk |

| P-CF8GB-266X-DVDC | 制造商:PNY Technologies 功能描述:OPTIMA PRO UDMA 8GB CF CARD - Bulk |

| PCF-A-03 | 制造商:Adam Technologies Inc 功能描述:03 Positions RECEPTACLE WITH BOARD HOOKS Top entry |

| PCFA-1GC02A-301N | 制造商:SMART Modular Technology Inc 功能描述:FLASH CARD WITH CONNECTOR - Trays |

| PCFA-1GC03AN-301 | 制造商:SMART Modular Technology Inc 功能描述:FLASH CARD WITH CONNECTOR - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。