- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382379 > PCD3316 (NXP Semiconductors N.V.) Caller-ID on Call Waiting CIDCW receiver PDF資料下載

參數(shù)資料

| 型號(hào): | PCD3316 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Caller-ID on Call Waiting CIDCW receiver |

| 中文描述: | 來(lái)電呼叫等待CIDCW編號(hào)接收機(jī) |

| 文件頁(yè)數(shù): | 12/30頁(yè) |

| 文件大?。?/td> | 534K |

| 代理商: | PCD3316 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

Philips Semiconductors

PCD3316

CIDCW receiver

Product specification

11 March 1999

12 of 30

9397 750 04824

Philips Electronics N.V. 1999. All rights reserved.

Unetited

The device that acknowledges must pull down the SDA line during the acknowledge

clock period immediately after the 8th SCL pulse, so that the SDA line is stable LOW

times must be taken into consideration).

A master receiver must signal an end of data to the transmitter by not generating an

acknowledge on the last byte that has been clocked out of the slave. In this event the

transmitter must leave the data line HIGH to enable the master to generate a STOP

condition.

7.12.5

I

2

C-bus protocol

Before any data is transmitted on the I

2

C-bus, the device which should respond is

addressed first. The addressing is always carried out with first byte transmitted after

the START procedure. One I

2

C-bus slave address is reserved for the PCD3316, E0H

(1110 0000 for write and 1110 0001 for read).

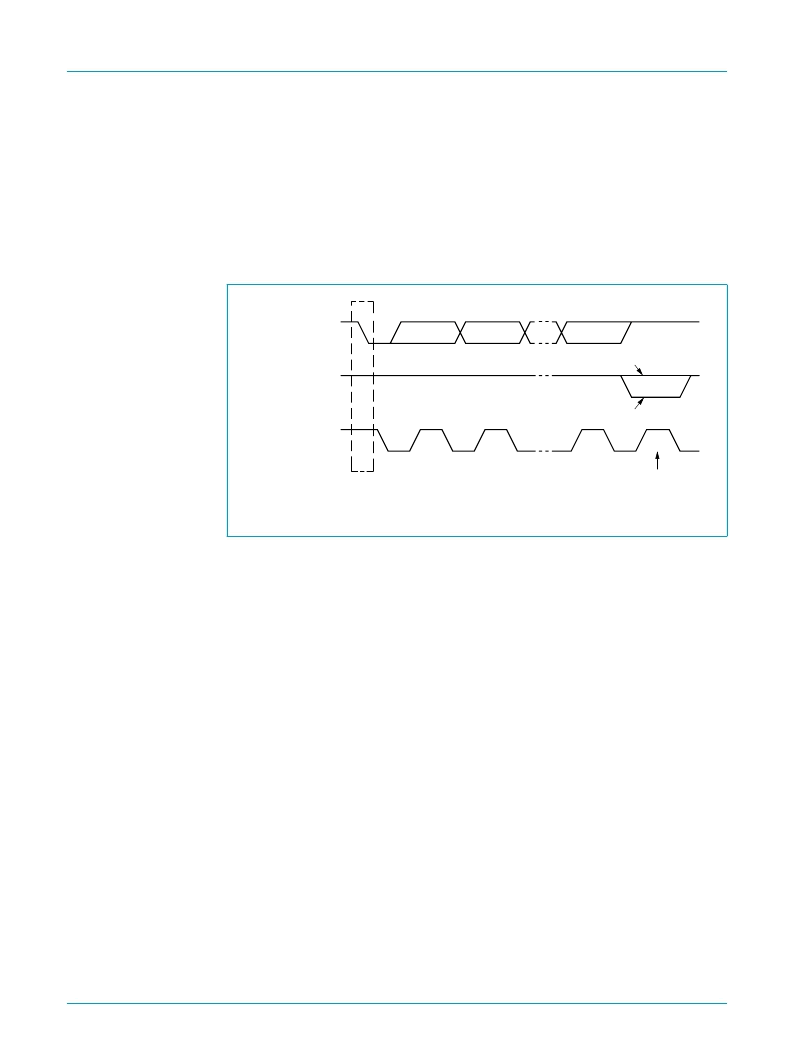

The I

C-bus protocol is shown in

Figure 13

. Two different sequences are considered,

the write sequence and the read sequence. Both sequences are initiated with a

START condition (S) from the I

2

C-bus master which is followed by the PCD3316 slave

address with the read bit cleared. The first byte after the I

2

C-bus address is

interpreted as the address of a PCD3316 register.During the write sequence the

register address of the PCD3316 is auto-incremented on each acknowledge. The

write sequence is ended with a STOP condition from the master. If the addressed

register is read-only or non-existent, nothing will be changed.

For the read sequence the bus master issues a repeated START condition followed

by the PCD3316 slave address with the read bit set. Then data is read from

previously set address and sent out. When the master responds with an acknowledge

the address of the register is auto incremented and the slave will put the data from

the next register on the bus. The read sequence is stopped when the master stops

giving an acknowledge and generates a STOP condition.

When a non-existing register is addressed the PCD3316 will return FFH. Existing

register addresses are shown in

Section 7.13

. An additional register address (73H) is

reserved for test purposes. This address cannot be reached with the auto-increment

function of the I

2

C-bus interface.

Fig 12. I

2

C-bus acknowledge.

idth

MBC602

S

START

condition

9

8

2

1

clock pulse for

acknowledgement

not acknowledge

acknowledge

DATA OUTPUT

BY TRANSMITTER

DATA OUTPUT

BY RECEIVER

SCL FROM

MASTER

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD3316T | Caller-ID on Call Waiting CIDCW receiver |

| PCD3330-1 | Multistandard repertory dialler/ringer with EEPROM |

| PCD3330-1P | Multistandard repertory dialler/ringer with EEPROM |

| PCD3330-1T | Multistandard repertory dialler/ringer with EEPROM |

| PCD3354AH | 8-bit microcontrollers with DTMF generator and 256 bytes EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD3316T | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Caller-ID on Call Waiting CIDCW receiver |

| PCD3316TD-T | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Caller Number ID Circuit |

| PCD3320CD | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Pulse Telephone Dialer |

| PCD3321CD | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Pulse Telephone Dialer |

| PCD3322CP | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Pulse Telephone Dialer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。