- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299585 > P4C1024-35C6M (PYRAMID SEMICONDUCTOR CORP) 128K X 8 STANDARD SRAM, 35 ns, CDIP32 PDF資料下載

參數(shù)資料

| 型號(hào): | P4C1024-35C6M |

| 廠商: | PYRAMID SEMICONDUCTOR CORP |

| 元件分類: | SRAM |

| 英文描述: | 128K X 8 STANDARD SRAM, 35 ns, CDIP32 |

| 封裝: | 0.600 INCH, SIDE BRAZED, CERAMIC, DIP-32 |

| 文件頁(yè)數(shù): | 10/14頁(yè) |

| 文件大?。?/td> | 152K |

| 代理商: | P4C1024-35C6M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

P4C1024

Page 5 of 14

Document # SRAM124 REV A

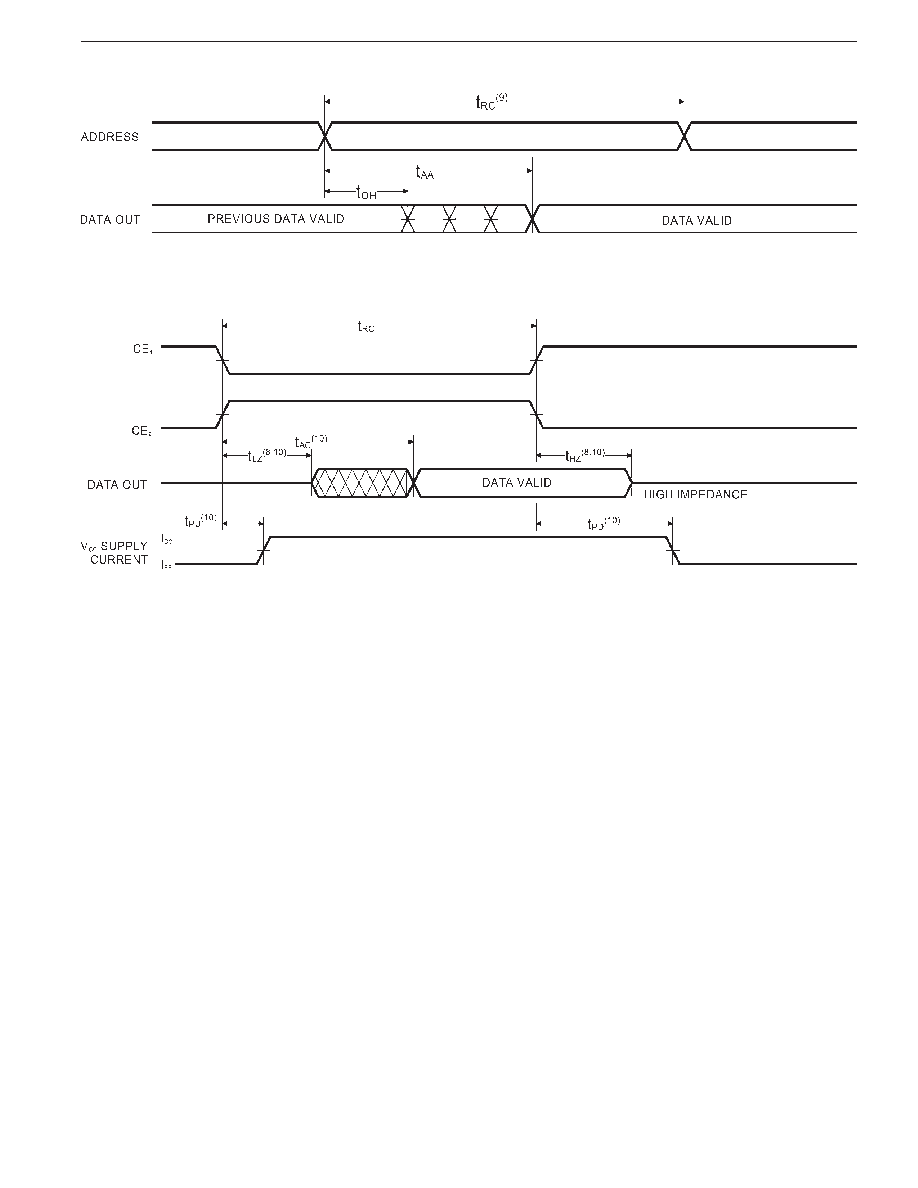

TIMINIG WAVERFORM OF READ CYCLE NO. 2 (ADDRESS CONTROLLED)(5,6)

TIMING WAVEFORM OF READ CYCLE NO. 3 (

CE

1, CE2 CONTROLLED)

(5,7,10)

Notes:

9. READ Cycle Time is measured from the last valid address to the first

transitioning address.

10. Transitions caused by a chip enable control have similar delays

irrespective of whether

CE

1 or CE2 causes them.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P4C1024L-100CJM | 128K X 8 STANDARD SRAM, 100 ns, CDSO32 |

| P4C1024L-45C4MB | 128K X 8 STANDARD SRAM, 45 ns, CDIP32 |

| P4C1024L-85C4M | 128K X 8 STANDARD SRAM, 85 ns, CDIP32 |

| P4C1256L-70PILF | 32K X 8 STANDARD SRAM, 70 ns, PDIP28 |

| P4C1256-20PI | 32K X 8 STANDARD SRAM, 20 ns, PDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P4C1024-35J3C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| P4C1024-35J3I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| P4C1024-35J4C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| P4C1024-35J4I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

| P4C1024-35P3C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。