- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄189002 > NAND01GR4B3CZA1E (STMICROELECTRONICS) 64M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 PDF資料下載

參數(shù)資料

| 型號: | NAND01GR4B3CZA1E |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | PROM |

| 英文描述: | 64M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 |

| 封裝: | 9.50 X 12 MM, 1 MM HEIGHT, 0.80 MM PITCH, ROHS COMPLIANT, VFBGA-63 |

| 文件頁數(shù): | 39/59頁 |

| 文件大?。?/td> | 998K |

| 代理商: | NAND01GR4B3CZA1E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

NAND512-B, NAND01G-B, NAND02G-B, NAND04G-B, NAND08G-B

44/59

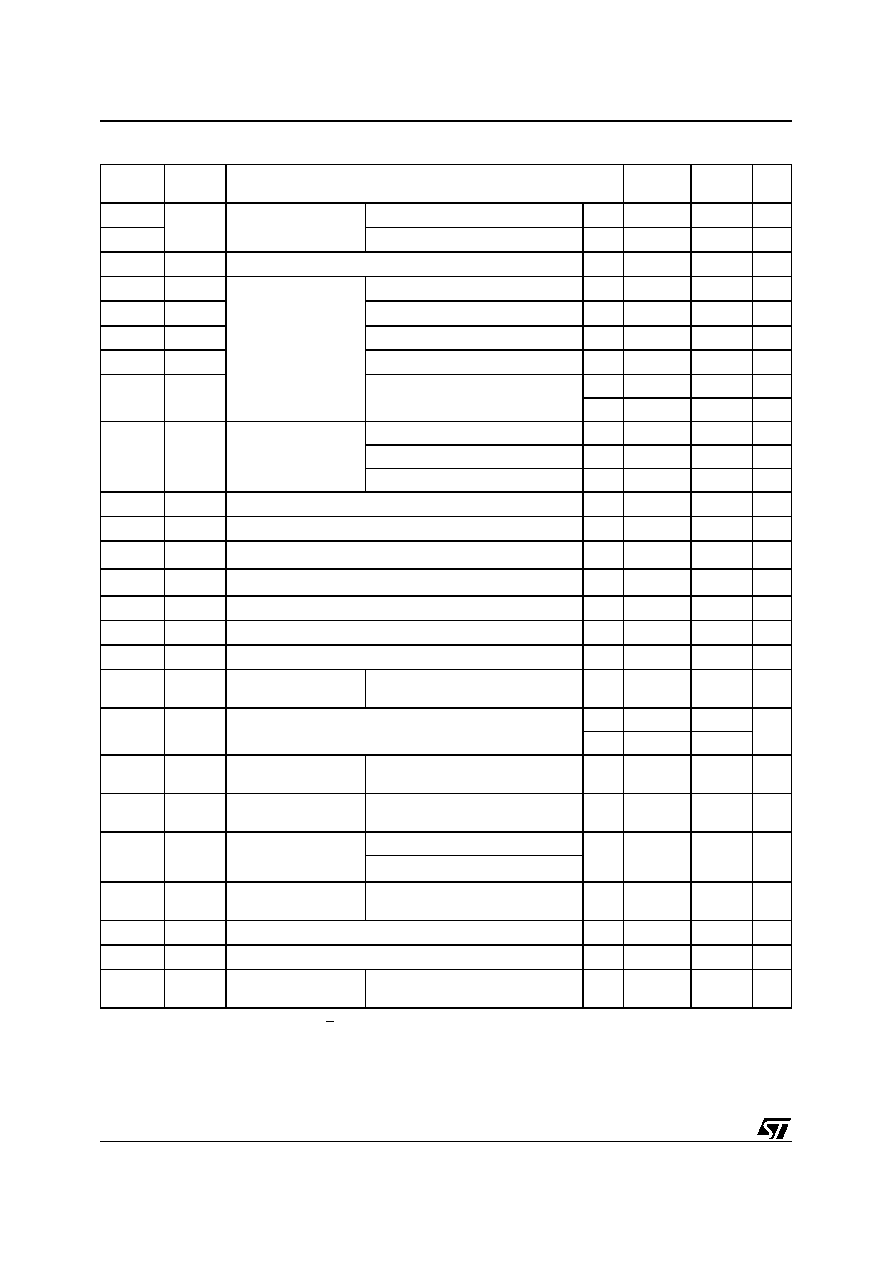

Table 25. AC Characteristics for Operations

Note: 1. The time to Ready depends on the value of the pull-up resistor tied to the Ready/Busy pin. See Figures 35, 36 and 37.

2. To break the sequential read cycle, E must be held High for longer than tEHEL.

3. ES = Electronic Signature.

Symbol

Alt.

Symbol

Parameter

1.8V

Devices

3V

Devices

Unit

tALLRL1

tAR

Address Latch Low to

Read Enable Low

Read Electronic Signature

Min

10

ns

tALLRL2

Read cycle

Min

10

ns

tBHRL

tRR

Ready/Busy High to Read Enable Low

Min

20

ns

tBLBH1

Ready/Busy Low to

Ready/Busy High

Read Busy time

Max

25

s

tBLBH2

tPROG

Program Busy time

Max

700

s

tBLBH3

tBERS

Erase Busy time

Max

3

ms

tBLBH4

Reset Busy time, during ready

Max

5

s

tBLBH5

tCBSY

Cache Busy time

Typ

3

s

Max

500

s

tWHBH1

tRST

Write Enable High to

Ready/Busy High

Reset Busy time, during read

Max

5

s

Reset Busy time, during program

Max

10

s

Reset Busy time, during erase

Max

500

s

tCLLRL

tCLR

Command Latch Low to Read Enable Low

Min

10

ns

tDZRL

tIR

Data Hi-Z to Read Enable Low

Min

0

ns

tEHBH

tCRY

Chip Enable High to Ready/Busy High (E intercepted read)

Max

60 + tr

(1)

60 + tr

(1)

ns

tEHEL

tCEH

Chip Enable High to Chip Enable Low(2)

Min

100

ns

tEHQZ

tCHZ

Chip Enable High to Output Hi-Z

Max

20

ns

tELQV

tCEA

Chip Enable Low to Output Valid

Max

45

ns

tRHBL

tRB

Read Enable High to Ready/Busy Low

Max

100

ns

tRHRL

tREH

Read Enable High to

Read Enable Low

Read Enable High Hold time

Min

20

ns

tRHQZ

tRHZ

Read Enable High to Output Hi-Z

Min

15

ns

Max

30

tRLRH

tRP

Read Enable Low to

Read Enable High

Read Enable Pulse Width

Min

25

ns

tRLRL

tRC

Read Enable Low to

Read Enable Low

Read Cycle time

Min

60

50

ns

tRLQV

tREA

Read Enable Low to

Output Valid

Read Enable Access time

Max

35

ns

Read ES Access time(3)

tWHBH

tR

Write Enable High to

Ready/Busy High

Read Busy time

Max

25

s

tWHBL

tWB

Write Enable High to Ready/Busy Low

Max

100

ns

tWHRL

tWHR

Write Enable High to Read Enable Low

Min

60

ns

tWLWL

tWC

Write Enable Low to

Write Enable Low

Write Cycle time

Min

60

50

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NAND01GR4B3CZA6E | 64M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 |

| NAND01GW4B3BN6T | 64M X 16 FLASH 3V PROM, 35 ns, PDSO48 |

| NAND01GW4B3CZA1E | 64M X 16 FLASH 3V PROM, 35 ns, PBGA63 |

| NAND08GR4B2BZC6T | 512M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 |

| NAND08GR4B3BN1 | 512M X 16 FLASH 1.8V PROM, 35 ns, PDSO48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| NAND01GR4M0AZB5E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

| NAND01GR4M0AZB5F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

| NAND01GR4M0AZC5E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

| NAND01GR4M0AZC5F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

| NAND01GR4M0BZB5E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。