- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382352 > MTV016 (Electronic Theatre Controls, Inc.) Enhanced On-Screen-Display Controller PDF資料下載

參數(shù)資料

| 型號: | MTV016 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Enhanced On-Screen-Display Controller |

| 中文描述: | 增強的屏幕顯示控制器 |

| 文件頁數(shù): | 5/11頁 |

| 文件大小: | 104K |

| 代理商: | MTV016 |

MYSON

TECHNOLOGY

MTV016

MTV016 Revision 2.0 01/01/1999

5/11

character line displays is shown in Tables 2 and 3. The programmable vertical size range is 180 lines to

a maximum of 1420 lines.

The vertical display center for a full screen display may be figured out according to the information of the

vertical starting position register (VERTD) and VFLB input. The vertical delay starting from the leading

edge of VFLB is calculated using the following equation:

vertical delay time = (VERTD * 4 + 1) * H

H = one horizontal line display time

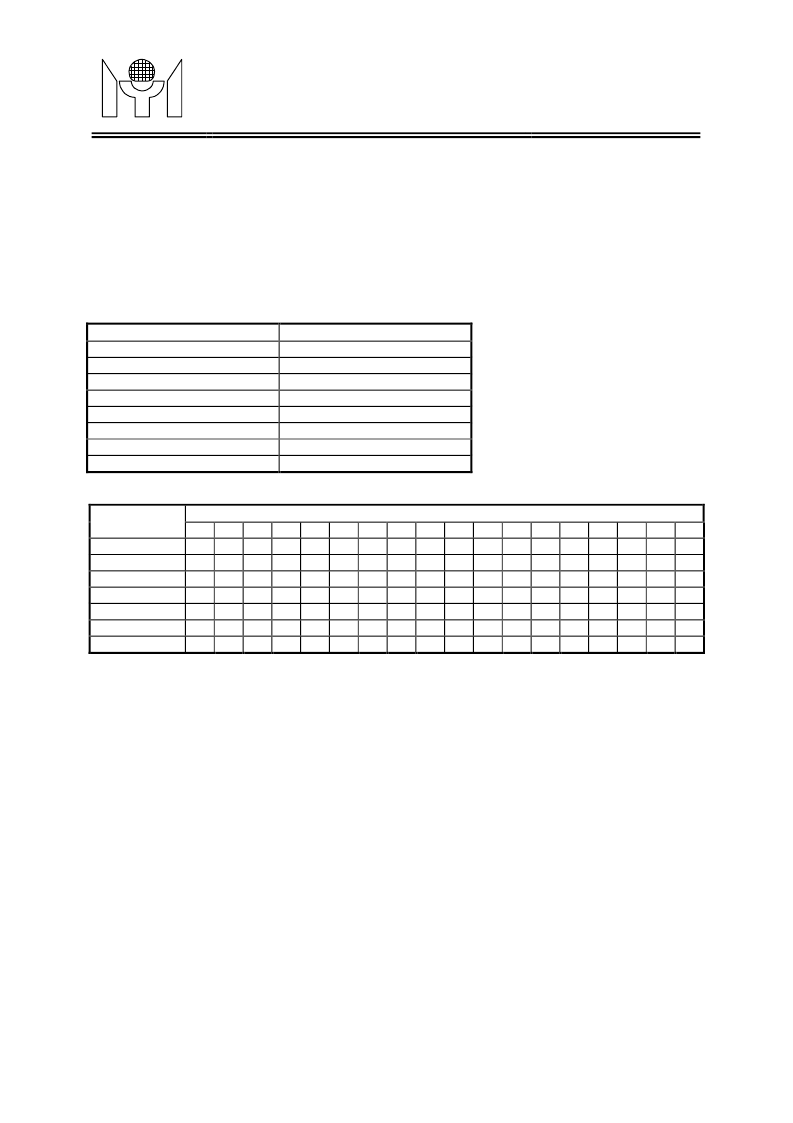

Table 2. Repeat Line Weight of Character

CH6 - CH0

CH6,CH5=11

CH6,CH5=10

CH6,CH5=0x

CH4=1

CH3=1

CH2=1

CH1=1

CH0=1

Repeat Line Weight

+18*3

+18*2

+18

+16

+8

+4

+2

+1

Table 3. Repeat Line Number of Character

Repeat Line

Weight

0

+1

-

+2

-

+4

-

+8

-

+16

-

+17

v

+18

v

Note:" v " means the nth line in the character would be repeated once, while " - " means the nth line in the character would not be

repeated.

Repeat Line #

7

8

-

v

-

-

-

-

v

-

v

v

v

v

v

v

1

-

-

-

v

v

v

v

2

-

-

v

-

v

v

v

3

-

-

-

v

v

v

v

4

-

v

-

-

v

v

v

5

-

-

-

v

v

v

v

6

-

-

v

-

v

v

v

9

-

-

-

v

v

v

v

10

-

-

v

-

v

v

v

11

-

-

-

v

v

v

v

12

-

v

-

-

v

v

v

13

-

-

-

v

v

v

v

14

-

-

v

-

v

v

v

15

-

-

-

v

v

v

v

16

-

-

-

-

v

v

v

17

-

-

-

-

-

-

v

3.4 Horizontal Display Control

The horizontal display control is used to generate control timing for horizontal displays based on double

character width bit (CWS), horizontal positioning register (HORD), horizontal resolution register (HORR)

and HFLB input. A horizontal display line consists of (HORR*12) dots, including 288 dots for 24 display

characters; the remaining dots are for a blank region. The horizontal delay starting from the HFLB

leading edge is calculated using the following equation:

horizontal delay time = (HORD * 6 + 49) * P - phase error detection pulse width

P = one pixel display time = one horizontal line display time / (HORR*12)

3.5 Phase Lock Loop (PLL)

On-chip PLL generates system clock timing (VCLK) by tracking the input HFLB and horizontal resolution

register (HORR). The frequency of VCLK is determined using the following equation:

VCLK Freq = HFLB Freq * HORR * 12

The VCLK frequency ranges from 5MHz to 90MHz and is selected by VCO1and VCO0. In addition,

when HFLB input is not present for MTV016, the PLL will generate a specific system clock,

approximately 2.5MHz, by a built-in oscillator to ensure data integrity.

3.6 Display & Row Control Registers

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTV030 | On-Screen Display with Auto-Sizing Controller |

| MTV112M | 8051 Embedded CRT Monitor Controller Flash Version |

| MTV118 | On-Screen-Display for LCD Monitor |

| MTV121 | Super On-Screen-Display for LCD Monitor |

| MUA08A | 265mW at 3.3V Supply Audio Power Amplifier with Shutdown Mode |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MTV016N-10 | 制造商:Myson Century Inc 功能描述:IC, PDIP16 |

| MTV016N-18 | 制造商:Myson Century Inc 功能描述:IC, PDIP16 |

| MTV018 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Super On-Screen-Display |

| MTV021 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced Super On-Screen Display |

| MTV021N20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced Super On-Screen Display |

發(fā)布緊急采購,3分鐘左右您將得到回復。