- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382352 > MTV016 (Electronic Theatre Controls, Inc.) Enhanced On-Screen-Display Controller PDF資料下載

參數(shù)資料

| 型號(hào): | MTV016 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Enhanced On-Screen-Display Controller |

| 中文描述: | 增強(qiáng)的屏幕顯示控制器 |

| 文件頁數(shù): | 1/11頁 |

| 文件大小: | 104K |

| 代理商: | MTV016 |

MYSON

TECHNOLOGY

Enhanced On-Screen-Display Controller

MTV016

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without

notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

MTV016 Revision 2.0 01/01/1999

1/11

FEATURES

Horizontal SYNC input up to 100 KHz.

On-chip PLL circuitry up to a 90 MHz pixel rate for multi-SYNC operation.

Programmable horizontal resolutions up to 1524 dots per display row.

538-byte display registers to control full screen display.

Full screen display consists of 10 (rows) by 24 (columns) characters.

12 x 18 dot matrix per character.

128 built-in characters and graphic symbols, and character by character color selection.

Maximum of 8 colors selectable per display row.

Double character height and/or width control.

Programmable positioning for display screen center.

Bordering and shadowing effect for display.

Programmable vertical character height (18 to 71 lines) for multi-SYNC operation.

4 programmable background windows with multi-level windowing effect.

Software clear function for display frame buffer.

HSYNC and VSYNC input polarity selectable.

Auto detection for input edge distortion between HSYNC and VSYNC inputs.

Half tone and fast blanking output.

Software force blank function for display frame.

Compatible with both SPI bus and I

2

C interface through pin selection.

16-pin PDIP package.

GENERAL DESCRIPTION

MTV016 is designed for use in monitor applications to display the built-in characters or symbols onto a

monitor screen. The display operation occurs by transferring data and control information in the micro-

controller to RAM through a serial data interface. It can execute a full screen display automatically and

specific functions such as character bordering, shadowing, double height and width, font by font color

control, frame positioning, frame size control by character height and horizontal display resolution, and

windowing effect.

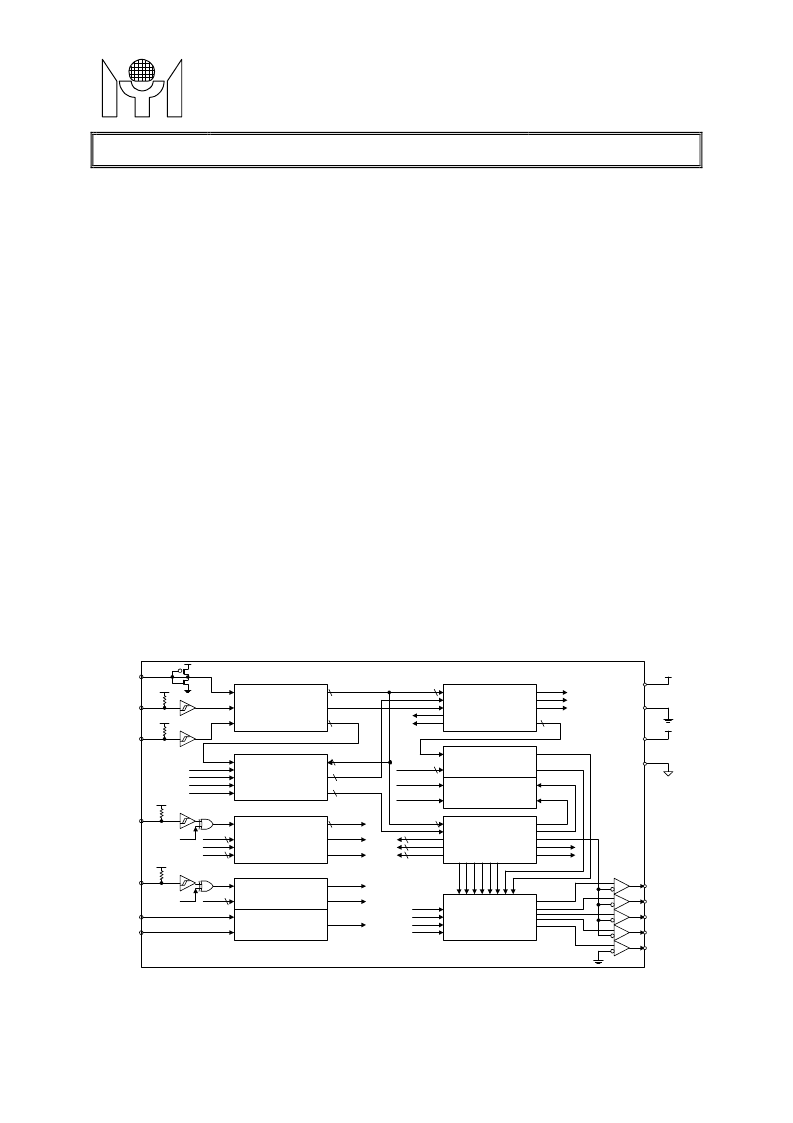

BLOCK DIAGRAM

SERIAL DATA

INTERFACE

ADDRESS BUS

ADMINISTRATOR

VERTICAL

DISPLAY

CONTROL

DISPLAY & ROW

CONTROL

REGISTERS

COLOUR

ENCODER

WINDOWS &

FRAME

CONTROL

W

W

W

C

F

B

CCS0

CCS1

BLINK

VCLKX

DATA

VERTD

HORD

CH

8

8

7

BSEN

SHADOW

OSDENB

HSP

VSP

HORIZONTAL

DISPLAY CONTROL

PHASE LOCK LOOP

8

LPN

CWS

VCLKS

5

DATA

CWS

CHS

5

CCS0

CCS1

BLINK

CRADDR

7

LUMA

BORDER

ARWDB

HDREN

VCLKX

HORD 7

CH

CHS

VERTD

7

8

LPN

NROW

VDREN

5

RCADDR

DADDR

WADDR

5

9

5

ARWDB

HDREN

VDREN

NROW

DATA

DAEN

RAEN,CAEN

8

2

CHARACTER ROM

LUMINANCE &

BORDGER

GENERATOR

VDD

VSS

VDDA

VSSA

ROUT

GOUT

BOUT

FBKG

HTONE

HFLB

RP

VCO

VFLB

SSB

SCK

SDA

VSP

HSP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTV030 | On-Screen Display with Auto-Sizing Controller |

| MTV112M | 8051 Embedded CRT Monitor Controller Flash Version |

| MTV118 | On-Screen-Display for LCD Monitor |

| MTV121 | Super On-Screen-Display for LCD Monitor |

| MUA08A | 265mW at 3.3V Supply Audio Power Amplifier with Shutdown Mode |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MTV016N-10 | 制造商:Myson Century Inc 功能描述:IC, PDIP16 |

| MTV016N-18 | 制造商:Myson Century Inc 功能描述:IC, PDIP16 |

| MTV018 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Super On-Screen-Display |

| MTV021 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced Super On-Screen Display |

| MTV021N20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced Super On-Screen Display |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。