- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359730 > MC9328MX21CVM (Motorola, Inc.) i.MX family of microprocessors PDF資料下載

參數(shù)資料

| 型號: | MC9328MX21CVM |

| 廠商: | Motorola, Inc. |

| 英文描述: | i.MX family of microprocessors |

| 中文描述: | i.MX系列微處理器 |

| 文件頁數(shù): | 88/96頁 |

| 文件大?。?/td> | 1495K |

| 代理商: | MC9328MX21CVM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁當前第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

相關PDF資料 |

PDF描述 |

|---|---|

| MC68HC711E9CFN2 | Microcontrollers |

| MC68HC711E9CFN3 | Microcontrollers |

| MC68HC711E9CFS2 | Microcontrollers |

| MC68HC711E9CFS3 | Microcontrollers |

| MC68HC11A0CFN3 | HCMOS Single-Chip Microcontroller |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

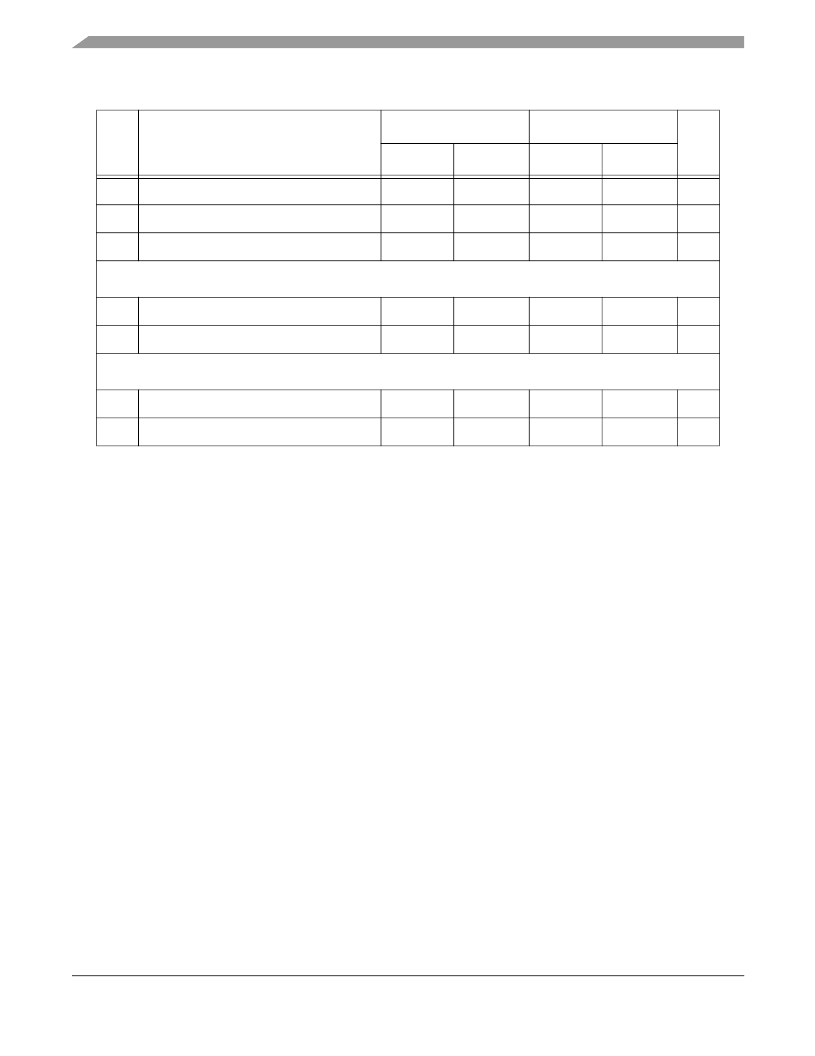

| MC9328MX21CVM | 制造商:Freescale Semiconductor 功能描述:Microprocessor |

| MC9328MX21CVMR2 | 功能描述:處理器 - 專門應用 DB I.MX21 17X17 PB-FR RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MC9328MX21DVG | 制造商:Rochester Electronics LLC 功能描述:DB I.MX21 - Bulk 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

| MC9328MX21DVGR2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC9328MX21DVH | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:i.MX family of microprocessors |

發(fā)布緊急采購,3分鐘左右您將得到回復。