- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370826 > M2S28D40ATP-75 (Mitsubishi Electric Corporation) 128M Double Data Rate Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M2S28D40ATP-75 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 128M Double Data Rate Synchronous DRAM |

| 中文描述: | 128M的雙數(shù)據(jù)速率同步DRAM |

| 文件頁(yè)數(shù): | 17/36頁(yè) |

| 文件大小: | 1216K |

| 代理商: | M2S28D40ATP-75 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

17

MITSUBISHI ELECTRIC

Jun,'00

Preliminary

MITSUBISHI LSIs

DDR SDRAM (Rev.0.1)

M2S28D20/ 30/ 40ATP

128M Double Data Rate Synchronous DRAM

-75

105

-10

95

x4

x8

110

105

x16

120

115

x4

110

100

x8

115

110

x16

135

130

x4

60

55

x8

65

60

x16

75

70

x4

150

140

x8

170

160

x16

210

200

x4

145

135

x8

165

155

x16

200

180

IDD5

AUTO REFRESH CURRENT: t RC = t RFC (MIN)

x4/x8/x16

190

180

IDD6

SELF REFRESH CURRENT: CKE < 0.2V

x4/x8/x16

3

3

9

x4/x8/x16

40

40

Limits(Max.)

mA

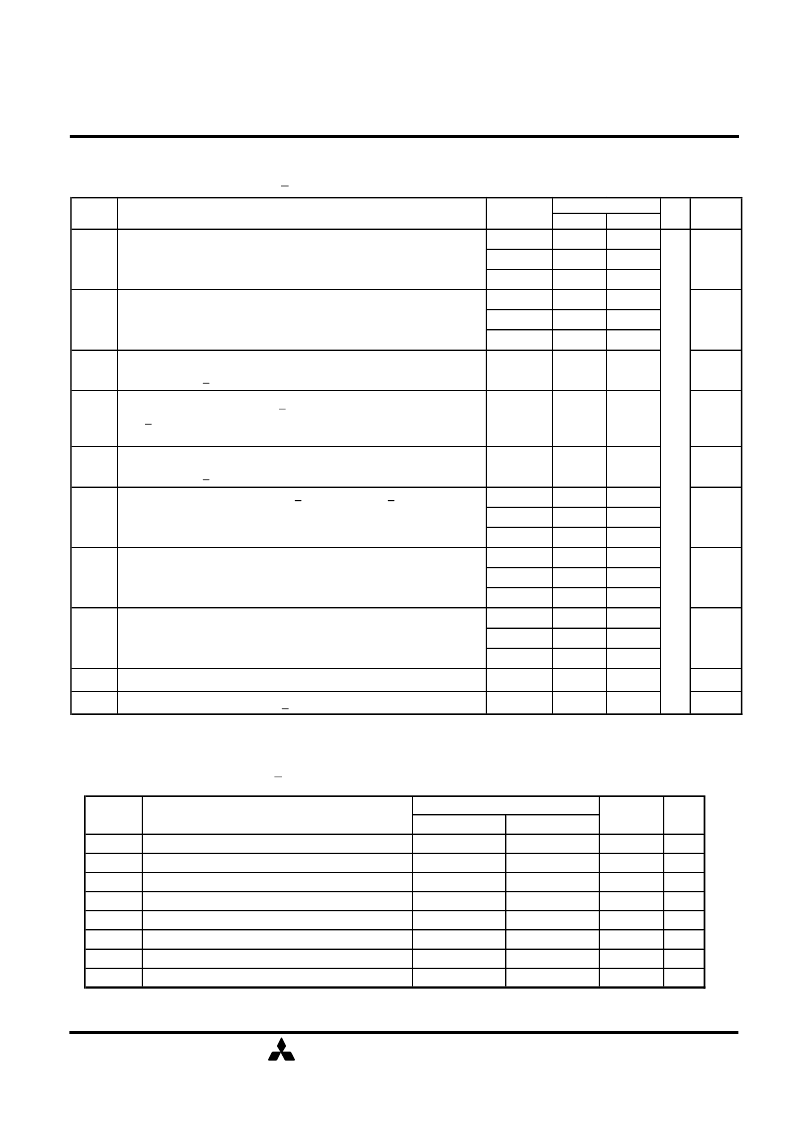

Symbol

Organization

Parameter/Test Conditions

IDD4R

OPERATING CURRENT: Burst = 2; Reads; Continuous burst;One bank active;

Address and control inputs changing once per clock cycle;CL=2.5; t CK = t CK

MIN; IOUT = 0 mA

PRECHARGE POWER-DOWN STANDBY CURRENT: All banks idle; power-

down mode; CKE <VIL (MAX); t CK = t CK MIN

x4/x8/x16

IDD2P

IDD2N

IDLE STANDBY CURRENT: /CS > VIH (MIN); All banks idle;

CKE > VIH (MIN); t CK = t CK MIN; Address and other control inputs changing

once per clock cycle

IDD4W

OPERATING CURRENT: Burst = 2; Writes; Continuous burst; One bank active;

Address and control inputs changing once per clock cycle; CL=2.5; t CK = t CK

MIN;DQ, DM and DQS inputs changing twice per clock cycle

IDD3P

ACTIVE POWER-DOWN STANDBY CURRENT: One bank active; power-

down mode; CKE < VIL (MAX); t CK = t CK MIN

ACTIVE STANDBY CURRENT: /CS > VIH (MIN); CKE > VIH (MIN); One

bank; Active-Precharge; t RC = t RAS MAX; t CK = t CK MIN; DQ,DM and

DQS inputs changing twice per clock cycle; address and other control inputs

changing once per clock cycle

IDD3N

x4/x8/x16

OPERATING CURRENT: One Bank; Active-Precharge; t RC = t RC MIN; t CK

= t CK MIN; DQ, DM and DQS inputs changing twice per clock cycle; address

and control inputs changing once per clock cycle

IDD0

IDD1

OPERATING CURRENT: One Bank; Active-Read-Precharge;

Burst = 2; t RC = t RC MIN; CL = 2.5; t CK = t CK MIN; IOUT= 0mA;

Address and control inputs changing once per clock cycle

40

40

Unit

Notes

20

20

AVERAGE SUPPLY CURRENT from Vdd

(Ta=0 ~ 70

o

C, Vdd = VddQ = 2.5V + 0.2V, Vss = VssQ = 0V, Output Open, unless otherwise noted)

AC OPERATING CONDITIONS AND CHARACTERISTICS

(Ta=0 ~ 70

o

C, Vdd = VddQ = 2.5V + 0.2V, Vss = VssQ = 0V, Output Open, unless otherwise noted)

M in.

M ax.

VIH(AC ) High-Level Input Voltage (AC )

VIL(AC )

Low-Level Input Voltage (AC )

VID(AC ) Input Differential Voltage, C LK and /C LK

VIX(AC ) Input C rossing Point Voltage, C LK and /CLK

IO Z

O ff-state O utput C urrent /Q floating Vo=0~VddQ

II

Input C urrent / VIN =0 ~ VddQ

IO H

O utput High C urrent (VO UT = 1.95 V)

IO L

O utput High C urrent (VO UT = 0.35 V)

Vref + 0.35

Vref - 0.35

VddQ + 0.6

0.7

7

8

0.5*VddQ - 0.2 0.5*VddQ + 0.2

-5

-2

-16.8

16.8

5

2

μ

A

μ

A

mA

mA

N otes

Limits

Symbol

Parameter / Test C onditions

Unit

V

V

V

V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M2V28S20TP-6 | 128 x 64 pixel format, LED Backlight available |

| M2V28S30TP-6 | 128 x 64 pixel format, LED Backlight available |

| M2V28S40TP-6 | 128 x 64 pixel format, LED Backlight available |

| M2V28S40ATP-7 | 128M Synchronous DRAM |

| M2V28S40ATP-7L | 128M Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M2S28UC | 功能描述:閃存 MACH2 2.5" SATA SSD 8GB COM TEMP RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲(chǔ)類型:Flash 存儲(chǔ)容量:2 MB 結(jié)構(gòu):256 K x 8 定時(shí)類型: 接口類型:SPI 訪問時(shí)間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| M2S28UI | 制造商:STEC Inc 功能描述:8GB 2.5", SATA,I-TEMP,MACH2 - Bulk |

| M2S56D20AKT | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2S56D20AKT-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2S56D20AKT-10L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。