- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369884 > LXP710PE Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號: | LXP710PE |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 36/84頁 |

| 文件大?。?/td> | 1108K |

| 代理商: | LXP710PE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

LXP710

—

HDSL Framer/Mapper for 1168 kbps Applications

36

Datasheet

Read/Write

Note:

Although the HDSL overhead indicator bits are active Low on the HDSL data stream, all status bits

in this register are active High, i.e., the status bits are inverted from what was received on the loop.

Demux Loss of Signal Status Register

Address: 19

Abbreviation: DXLOSDSTAT

Read/Write

All of the HDSL overhead status bits in this register are latched active High when detected, and

remain High until a write of a logic one is done by the microprocessor.

Note:

Although the HDSL overhead indicator bits are active Low on the HDSL data stream, all status bits

in this register are active High, i.e., the status bits are inverted from what was received on the loop.

Loop Reversal Status Register

Address: 1A

Abbreviation: LPRSTAT

Read/Write

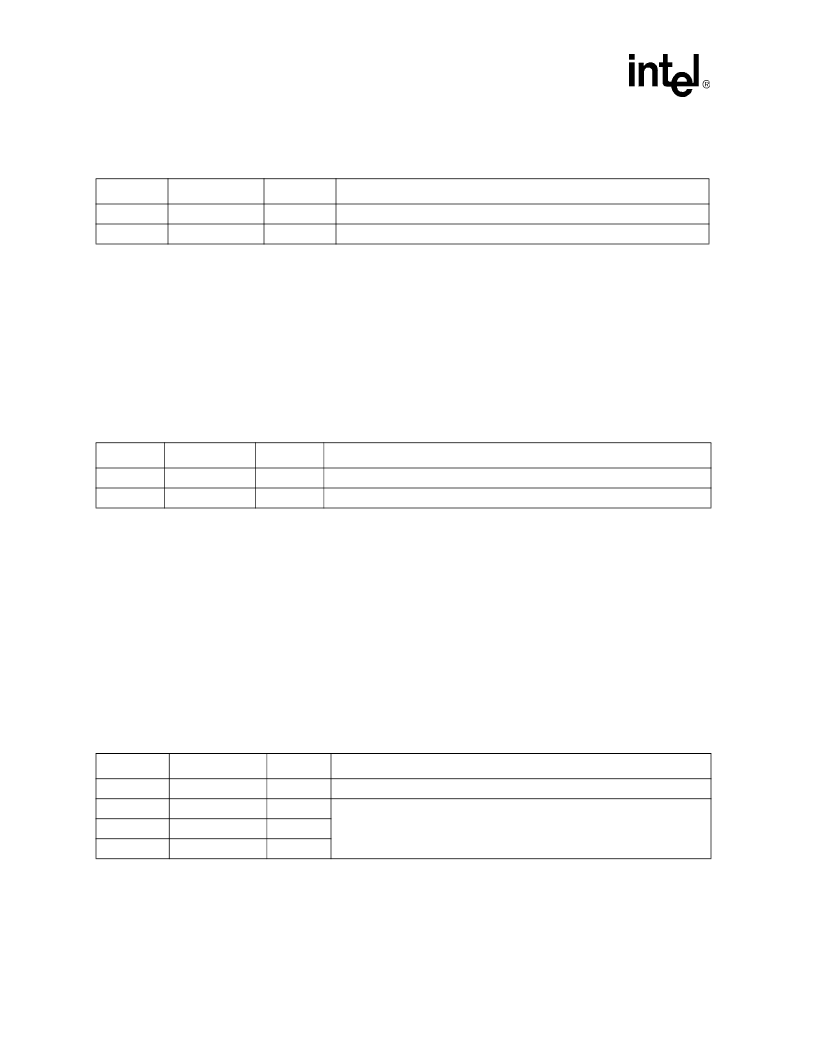

Table 26. Demux HDSL Repeater Present Status Register

Bit

Name

Default

Description

<7:3>

n/a

0

Not used; Always read Low.

<2:0>

D<3:1>HRP

0

Demux loop<3:1> HDSL Repeater present status bit.

Table 27. Demux Loss of Signal Status Register

Bit

Name

Default

Description

<7:3>

n/a

0

Not used; Always read Low.

<2:0>

D<3:1>LOSD

0

Demux loop<3:1> loss of signal status bit.

Table 28. Loop Reversal Status Register

Bit

Name

Default

Description

7, 6

n/a

0

Not used; Always read zero.

5

LPRDONE3

0

Loop Reversal Detect. When in HTUC Mode (LTU = 1), Loop

x

has detected

the loop identification returned from HTUR.

In HTUR Mode (LTU = 0), Loop

x

has detected the same loop identification

three times, and the Loop

x

reversal is done.

4

LPRDONE2

0

3

LPRDONE1

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXP730LE | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| LXT1000 | LAN TRANSCEIVER|SINGLE|HYBRID|BGA|492PIN|PLASTIC |

| LXT19908 | Amplifier. Other |

| LXT300JE | PCM Transceiver |

| LXT300NE | PCM Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXP730 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Multi-Rate DSL Framer |

| LXP730LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FRAMER/FORMATTER|CMOS|QFP|64PIN|PLASTIC |

| LXP80 | 制造商:Johnson Components 功能描述: |

| LXPB2SA-50SB-Q | 制造商:SMC Corporation of America 功能描述:Actuator, electric, ball bushing |

| LXPH0000 | 制造商:Red Lion Controls 功能描述:ANNUNCIATOR LABELS, 1 LPAX LABEL: PH 制造商:Red Lion Controls 功能描述:1 LPAX LABEL PH |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。