- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369842 > LSIFC929 LSIFC929 dual channel fibre solutions PDF資料下載

參數(shù)資料

| 型號(hào): | LSIFC929 |

| 英文描述: | LSIFC929 dual channel fibre solutions |

| 中文描述: | LSIFC929雙通道光纖解決方案 |

| 文件頁(yè)數(shù): | 47/144頁(yè) |

| 文件大?。?/td> | 1496K |

| 代理商: | LSIFC929 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)當(dāng)前第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)

4-7

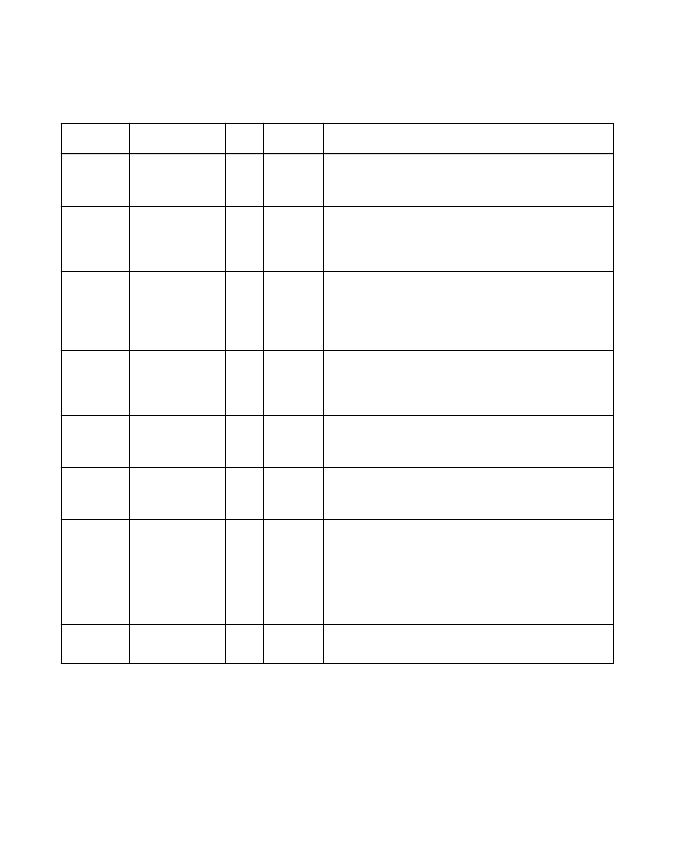

Table 4.2

describes the FC 10-bit Interface signals.

Table 4.2

FC 10-Bit Interface Signals

Name

BGA Pos

Type Strength Description

TX[9:0]

N4, P3, P2, P1,

R3, R2, R1, T3,

T2, T1

O

8 mA

10-bit parallel data

to the PHY serializer device.

Data is clocked out to the PHY on the rising edge of

TBC. These pads contain an internal 100

μ

A pull-up.

RX[9:0]

C1, C2, D1, D2,

D3, E1, E2, E3,

E4, F1

I

N/A

10-bit parallel data

from the PHY serializer device.

Data is clocked into the LSIFC909 on the rising

edge of RBC[0] and RBC[1]. These pads contain an

internal 100

μ

A pull-up.

EN_CDET

U1

O

4 mA

Enable Comma Detect.

This pin enables the

comma detect circuitry on the PHY device to

establish byte synchronization on the next comma

that is received. This pad contains an internal

100

μ

A pull-up.

EWRAP

R4

O

4 mA

Electrically Wrap.

This pin causes the PHY device

to electrically wrap the serialized transmit data to the

deserializer and disables the laser output, if present.

This pad contains an internal 100

μ

A pull-up.

LCK_REF/ B3

O

4 mA

Lock Reference.

This pin causes the PHY device to

lock its receiver PLL to the TBC. This pad contains

an internal 100

μ

A pull-up.

TBC

N2

O

8 mA

Transmit Buffered Clock.

A buffered version of the

REFCLK input that is phase aligned to the TX data.

This pad contains an internal 100

μ

A pull-up.

RBC[1:0]

G3, F2

I

N/A

Receive Buffered Clock Inputs.

RBC[0] is the

clock from the PHY device used to latch RX into the

protocol device. RBC[1] is an optional clock that is

180 degrees out of phase from RBC[0]. This clock is

used to latch alternate bytes for 10-bit interface

compliant modules. These pads contain an internal

100

μ

A pull-up.

RXLOS

B1

I

N/A

Received Signal Loss.

Gigabit Interface Converter

(GBIC) has detected loss of signal.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LSIFC929X | LSIFC929X dual channel fibre solutions |

| LSIU160 | LSIU160 Ultra160 SCSI host adapter |

| LSIU40HVD | LSIU40HVD PCI to Dual Channel SCSI host adapter user's guide v2.2 8/02 |

| LSIU40SE | LSIU40SE Dual Channel PCI to Ultra SCSI host adapter user's guide v2.2 8/02 |

| LSIU80LVD | LSIU80LVD Ultra2 LVD SCSI host adapter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LSIFC929-329BGA | 制造商:LSI Corporation 功能描述:Fiber Controller 456-Pin BGA |

| LSIFC929X | 制造商:LSI Corporation 功能描述:- Bulk |

| LSIFC929XL | 制造商:LSI Corporation 功能描述:2GB PCI-X TO DUAL CHANNEL - Bulk |

| LSIFC949X | 制造商:LSI Corporation 功能描述:PCI-X TO DUAL CHANNEL - Bulk |

| LSIFC949X A0 | 制造商:LSI 功能描述: 制造商:LSI Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。