- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299412 > LP62S4096E-I (AMIC Technology Corporation) 512K X 8 BIT LOW VOLTAGE CMOS SRAM PDF資料下載

參數(shù)資料

| 型號: | LP62S4096E-I |

| 廠商: | AMIC Technology Corporation |

| 英文描述: | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| 中文描述: | 為512k × 8位低電壓CMOS的SRAM |

| 文件頁數(shù): | 11/14頁 |

| 文件大?。?/td> | 162K |

| 代理商: | LP62S4096E-I |

LP62S4096E-T Series

(January, 2002, Version 2.0)

6

AMIC Technology, Inc.

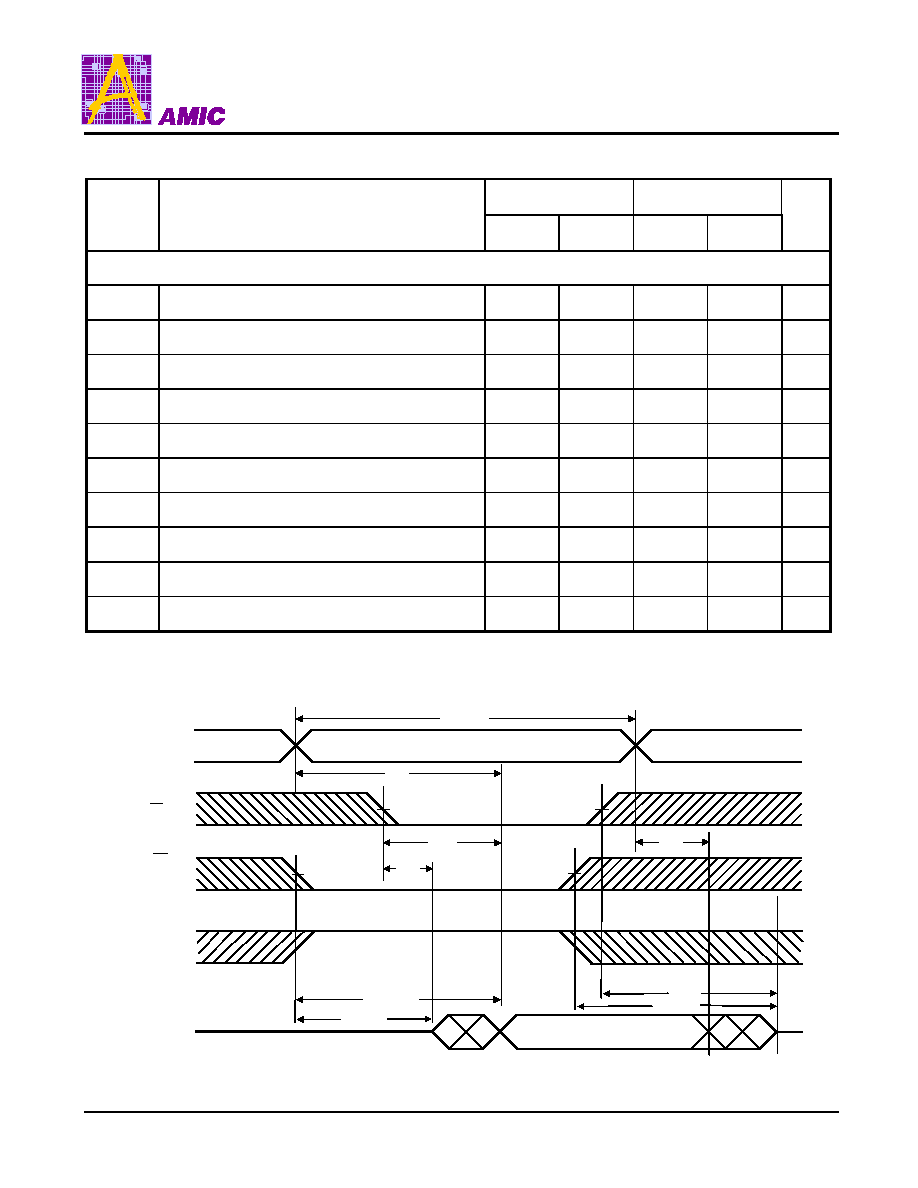

AC Characteristics (continued)

Symbol

Parameter

LP62S4096E-55LLT

LP62S4096E-70LLT

Unit

Min.

Max.

Min.

Max.

Write Cycle

tWC

Write Cycle Time

55

-

70

-

ns

tCW1

Chip Enable to End of Write

50

-

60

-

ns

tAS

Address Setup Time

0

-

0

-

ns

tAW

Address Valid to End of Write

50

-

60

-

ns

tWP

Write Pulse Width

40

-

50

-

ns

tWR

Write Recovery Time

0

-

0

-

ns

tWHZ

Write to Output in High Z

0

25

0

25

ns

tDW

Data to Write Time Overlap

25

-

30

-

ns

tDH

Data Hold from Write Time

0

-

0

-

ns

tOW

Output Active from End of Write

5

-

5

-

ns

Notes: tCHZ, tOHZ and tWHZ are defined as the time at which the outputs achieve the open circuit condition and are

not referred to output voltage levels.

Timing Waveforms

Read Cycle 1

(1)

tRC

Address

tAA

tOE

tOLZ5

tOH

OE

tOHZ5

DOUT

tACE1 , tACE2

tCHZ1 , tCHZ2

tCLZ1 , tCLZ2

CE1

CE2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LP62S4096E-T | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP8900TLE-3333 | DUAL OUTPUT, FIXED POSITIVE LDO REGULATOR, PBGA6 |

| LP8900TLE-AACB | DUAL OUTPUT, FIXED POSITIVE LDO REGULATOR, PBGA6 |

| LP8900TLX-3333 | DUAL OUTPUT, FIXED POSITIVE LDO REGULATOR, PBGA6 |

| LP8900TLX-AACB | DUAL OUTPUT, FIXED POSITIVE LDO REGULATOR, PBGA6 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LP62S4096E-T | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EU-55LLI | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EU-55LLT | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EU-70LLI | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EU-70LLT | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。