- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374256 > K4D551638F-TC36 (SAMSUNG SEMICONDUCTOR CO. LTD.) 256Mbit GDDR SDRAM PDF資料下載

參數(shù)資料

| 型號: | K4D551638F-TC36 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256Mbit GDDR SDRAM |

| 中文描述: | 片256Mbit GDDR SDRAM內(nèi)存 |

| 文件頁數(shù): | 3/16頁 |

| 文件大小: | 206K |

| 代理商: | K4D551638F-TC36 |

256M GDDR SDRAM

K4D551638F-TC

4M x 16Bit x 4 Banks Graphic Double Data Rate Synchronous DRAM

with Bi-directional Data Strobe and DLL

- 3 -

Rev 1.7 (June 2004)

Target Spec

The K4D551638F is 268,435,456 bits of hyper synchronous data rate Dynamic RAM organized as 4 x 4,194,304 words by

16 bits, fabricated with SAMSUNG

’

s high performance CMOS technology. Synchronous features with Data Strobe allow

extremely high performance up to 1.1GB/s/chip. I/O transactions are possible on both edges of the clock cycle. Range of

operating frequencies, programmable burst length and programmable latencies allow the device to be useful for a variety

of high performance memory system applications.

GENERAL DESCRIPTION

FEATURES

FOR 4M x 16Bit x 4 Bank GDDR SDRAM

ORDERING INFORMATION

1. K4D551638F-LC is the Lead Free package part number.

2. For the K4D551638F-TC60, VDD & VDDQ = 2.5V + 5%

3. For the K4D551638F-TC36, VDD & VDDQ = 2.8V + 0.1V

4. For the K4D551638F-TC33, VDD & VDDQ = 2.8V ~ 2.95V

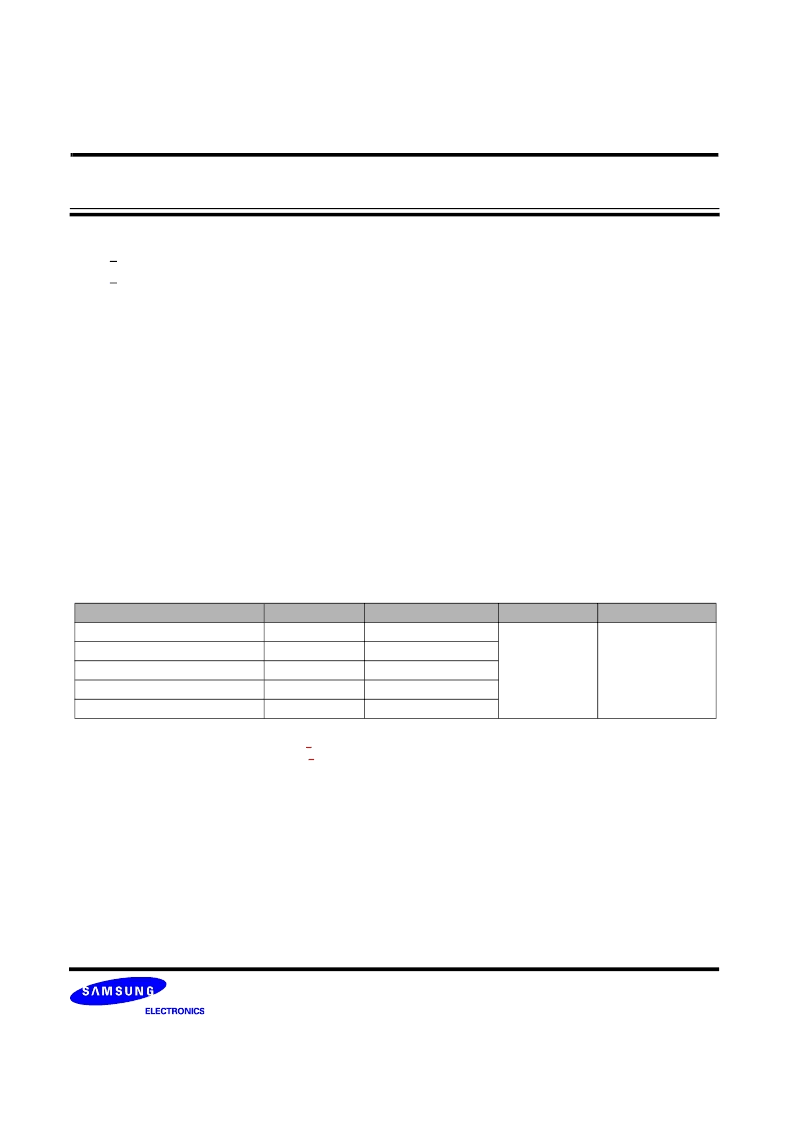

Part NO.

Max Freq.

Max Data Rate

Interface

Package

K4D551638F-TC33

300MHz

600Mbps/pin

SSTL_2

66pin TSOP-II

K4D551638F-TC36

275MHz

550Mbps/pin

K4D551638F-TC40

250MHz

500Mbps/pin

K4D551638F-TC50

200MHz

400Mbps/pin

K4D551638F-TC60*

166MHz

333Mbps/pin

2.6V + 0.1V power supply for device operation

2.6V + 0.1V power supply for I/O interface

SSTL_2 compatible inputs/outputs

4 banks operation

MRS cycle with address key programs

-. Read latency 3 (clock)

-. Burst length (2, 4 and 8)

-. Burst type (sequential & interleave)

All inputs except data & DM are sampled at the positive

going edge of the system clock

Differential clock input

No Write-Interrupted by Read Function

2 DQS’s ( 1DQS / Byte )

Data I/O transactions on both edges of Data strobe

DLL aligns DQ and DQS transitions with Clock transition

Edge aligned data & data strobe output

Center aligned data & data strobe input

DM for write masking only

Auto & Self refresh

64ms refresh period (8K cycle)

66pin TSOP-II

Maximum clock frequency up to 300MHz

Maximum data rate up to 600Mbps/pin

相關PDF資料 |

PDF描述 |

|---|---|

| K4D551638F-TC40 | 256Mbit GDDR SDRAM |

| K4D551638F-TC50 | 256Mbit GDDR SDRAM |

| K4D551638F-TC60 | 256Mbit GDDR SDRAM |

| K4D553235F-GC | 256M GDDR SDRAM |

| K4D553235F-GC25 | 256M GDDR SDRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| K4D551638F-TC40 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit GDDR SDRAM |

| K4D551638F-TC50 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit GDDR SDRAM |

| K4D551638F-TC50000 | 制造商:Samsung Semiconductor 功能描述:DRAM Chip GDDR SDRAM 256M-Bit 16Mx16 2.6V 66-Pin TSOP-II |

| K4D551638F-TC60 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit GDDR SDRAM |

| K4D553235F-GC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256M GDDR SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。