- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384545 > ISPPAC-CLK5610V-01TN48C (LATTICE SEMICONDUCTOR CORP) LED Ring Light; LED Color:Infrared; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:350mA; Supply Voltage:24VDC; Wavelength:880nm PDF資料下載

參數(shù)資料

| 型號: | ISPPAC-CLK5610V-01TN48C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | 時鐘及定時 |

| 英文描述: | LED Ring Light; LED Color:Infrared; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:350mA; Supply Voltage:24VDC; Wavelength:880nm |

| 中文描述: | 5600 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| 封裝: | LEAD FREE, TQFP-48 |

| 文件頁數(shù): | 24/47頁 |

| 文件大小: | 871K |

| 代理商: | ISPPAC-CLK5610V-01TN48C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

Lattice Semiconductor

ispClock5600 Family Data Sheet

24

end, the ispClock5600’s internal termination resistors are not available in these modes. Also note that output slew-

rate control is not available in LVDS or LVPECL mode, and that these drivers always operate at a

fi

xed slew-rate.

Polarity control (true/inverted) is available for all output drivers. In the case of single-ended output standards, the

polarity of each of the two output signals from each bank may be controlled independently. In the case of differen-

tial output standards, the polarity of the differential pair may be selected.

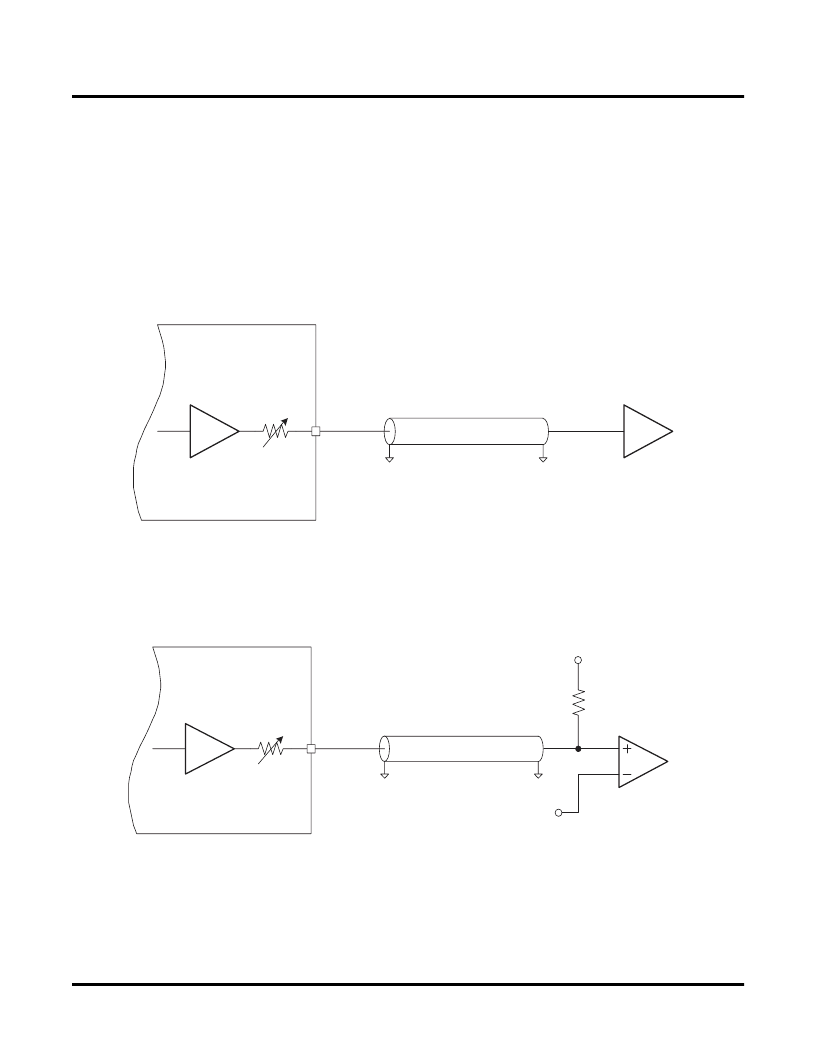

Suggested Usage

Figure 20 shows a typical con

fi

guration for the ispClock5600’s output driver when con

fi

gured to drive an LVTTL or

LVCMOS load. The ispClock5600’s output impedance should be set to match the characteristic impedance of the

transmission line being driven. The far end of the transmission line should be left open, with no termination resis-

tors.

Figure 20. Configuration for LVTTL/LVCMOS Output Modes

Figure 21 shows a typical con

fi

guration for the ispClock5600’s output driver when con

fi

gured to drive SSTL2,

SSTL3, or HSTL loads. The ispClock5600’s output impedance should be set to 40

for driving SSTL2 or SSTL3

loads and to the

≈

20

setting for driving HSTL. The far end of the transmission line must be terminated to an

appropriate VTT voltage through a 50

resistor.

Figure 21. Configuration for SSTL2, SSTL3, and HSTL Output Modes

While supporting single-ended HSTL and SSTL outputs, the ispClock5600 does not support differential HSTL or

SSTL outputs. Although complementary HSTL and SSTL signals may be generated by using both an inverted out-

put and a non-inverted output similarly con

fi

gured, the resulting signal pair may not meet the JEDEC differential

HSTL speci

fi

cations for common mode voltage or crossover voltage.

Figure 22 shows a typical con

fi

guration for the ispClock5600’s output driver when con

fi

gured to drive LVDS or dif-

ferential LVPECL loads. The ispClock5600’s output impedance is disengaged when the driver is set to LVDS or

Zo

Ro = Zo

ispClock5600

LVCMOS/LVTTL

Mode

LVCMOS/LVTTL

Receiver

Zo=50

Ro : 40 (SSTL)

≈

20

(HSTL)

ispClock5600

SSTL/HSTL

Mode

SSTL/HSTL

Receiver

VTT

VREF

RT=50

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPPAC-CLK5620V-01TN48C | LED Area Light; LED Color:Red; Leaded Process Compatible:No; Light Emitting Area:62x62mm; Peak Reflow Compatible (260 C):No; Supply Current:200mA; Supply Voltage:24VDC; Wavelength:630nm |

| ISPPAC-CLK5610V-01TN48I | Backlight LED; Color:Red; Digit/Alpha Height:70mm; Forward Current:250mA; Operating Temperature Range:0 C to +50 C; Leaded Process Compatible:No; Light Emitting Area:70x70mm; Peak Reflow Compatible (260 C):No; Supply Current:250mA |

| ISPPAC-CLK5620V-01TN48I | Backlight LED; Color:Red; Digit/Alpha Height:85mm; Forward Current:500mA; Operating Temperature Range:0 C to +50 C; Leaded Process Compatible:No; Light Emitting Area:85x220mm; Peak Reflow Compatible (260 C):No |

| ISPPAC-POWR1014 | In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

| ISPPAC-POWR1014-01T48I | In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPPAC-CLK5610V-01TN48I | 功能描述:時鐘驅(qū)動器及分配 PROGRAMMABLE ZERO DELAY CL GEN RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| ispPAC-CLK5620AV-01T100C | 功能描述:時鐘驅(qū)動器及分配 ISP 0 Delay Clock Ge n w/Unv Fan-Out Buf RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| ISPPACCLK5620AV-01T100C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Enhanced Zero-Delay, Clock Generator with Universal Fan-Out Buffer |

| ispPAC-CLK5620AV-01T100I | 功能描述:時鐘驅(qū)動器及分配 ISP 0 Dlay Clck Gen w/Unv Fan-Out Buf I RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| ISPPACCLK5620AV-01T100I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Enhanced Zero-Delay, Clock Generator with Universal Fan-Out Buffer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。