- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄9890 > IDT72T7295L5BB (IDT, Integrated Device Technology Inc)IC FIFO 32768X72 5NS 324-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72T7295L5BB |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 24/53頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FIFO 32768X72 5NS 324-BGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | 72T |

| 訪問(wèn)時(shí)間: | 5ns |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 324-BGA |

| 供應(yīng)商設(shè)備封裝: | 324-PBGA(19x19) |

| 包裝: | 托盤(pán) |

| 其它名稱: | 72T7295L5BB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

30

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72T7285/72T7295/72T72105/72T72115 2.5V TeraSync

72-BIT FIFO

16,384 x 72, 32,768 x 72, 65,536 x 72, 131,072 x 72

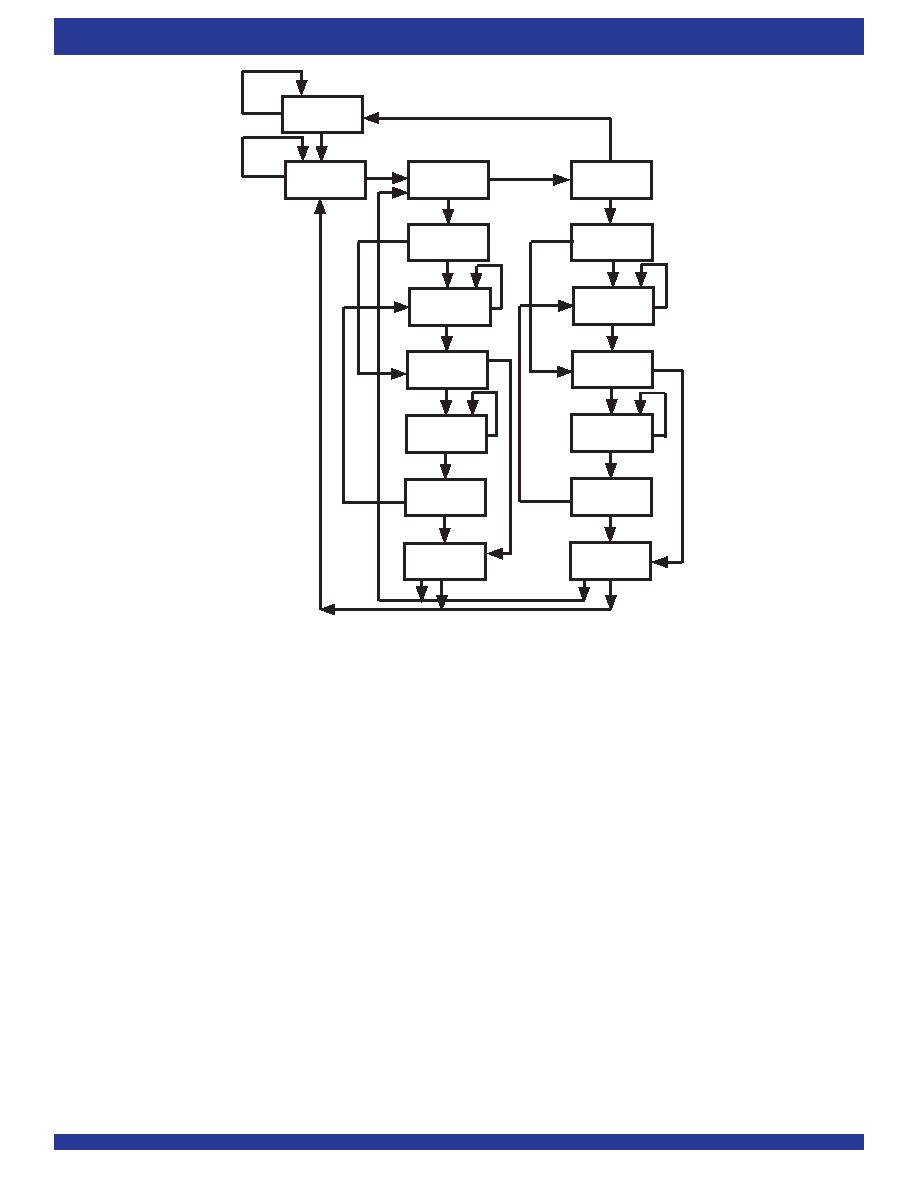

Figure 8. TAP Controller State Diagram

Test-Logic

Reset

Run-Test/

Idle

1

0

Select-

DR-Scan

Select-

IR-Scan

1

Capture-IR

0

Capture-DR

0

EXit1-DR

1

Pause-DR

0

Exit2-DR

1

Update-DR

1

Exit1-IR

1

Exit2-IR

1

Update-IR

1

0

1

5994 drw13

0

Shift-DR

0

Shift-IR

0

Pause-IR

0

1

Input = TMS

0

1

Refer to the IEEE Standard Test Access Port Specification (IEEE Std.

1149.1) for the full state diagram

All state transitions within the TAP controller occur at the rising edge of the

TCLK pulse. The TMS signal level (0 or 1) determines the state progression

that occurs on each TCLK rising edge. The TAP controller takes precedence

over the FIFO memory and must be reset after power up of the device. See

TRST description for more details on TAP controller reset.

Test-Logic-ResetAlltestlogicisdisabledinthiscontrollerstateenablingthe

normaloperationoftheIC.TheTAPcontrollerstatemachineisdesignedinsuch

awaythat,nomatterwhattheinitialstateofthecontrolleris,theTest-Logic-Reset

state can be entered by holding TMS at high and pulsing TCK five times. This

is the reason why the Test Reset (

TRST) pin is optional.

Run-Test-Idle In this controller state, the test logic in the IC is active only if

certaininstructionsarepresent.Forexample,ifaninstructionactivatestheself

test, then it will be executed when the controller enters this state. The test logic

in the IC is idles otherwise.

Select-DR-Scan This is a controller state where the decision to enter the

Data Path or the Select-IR-Scan state is made.

Select-IR-Scan This is a controller state where the decision to enter the

InstructionPathismade.TheControllercanreturntotheTest-Logic-Resetstate

other wise.

Capture-IR In this controller state, the shift register bank in the Instruction

Register parallel loads a pattern of fixed values on the rising edge of TCK. The

last two significant bits are always required to be “01”.

Shift-IR In this controller state, the instruction register gets connected

betweenTDIandTDO,andthecapturedpatterngetsshiftedoneachrisingedge

ofTCK.TheinstructionavailableontheTDIpinisalsoshiftedintotheinstruction

register.

Exit1-IR ThisisacontrollerstatewhereadecisiontoentereitherthePause-

IR state or Update-IR state is made.

Pause-IR This state is provided in order to allow the shifting of instruction

register to be temporarily halted.

Exit2-DR This is a controller state where a decision to enter either the Shift-

IR state or Update-IR state is made.

Update-IR In this controller state, the instruction in the instruction register is

latched in to the latch bank of the Instruction Register on every falling edge of

TCK. This instruction also becomes the current instruction once it is latched.

Capture-DR In this controller state, the data is parallel loaded in to the data

registers selected by the current instruction on the rising edge of TCK.

Shift-DR, Exit1-DR, Pause-DR, Exit2-DR and Update-DR These

controller states are similar to the Shift-IR, Exit1-IR, Pause-IR, Exit2-IR and

Update-IR states in the Instruction path.

NOTES:

1. Five consecutive TCK cycles with TMS = 1 will reset the TAP.

2. TAP controller does not automatically reset upon power-up. The user must provide a reset to the TAP controller (either by

TRST or TMS).

3. TAP controller must be reset before normal FIFO operations can begin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27466T21F16S | CONN RCPT 16POS WALL MT W/SCKT |

| MS27474E14A5P | CONN RCPT 5POS JAM NUT W/PINS |

| IDT72T72115L10BB | IC FIFO 131072X72 10NS 324-BGA |

| D38999/20WF11SN | CONN RCPT 11POS WALL MNT W/SCKT |

| MS3101E20-8S | CONN RCPT 6POS FREE HNG W/SCKT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72T7295L6-7BB | 功能描述:IC FIFO 32768X72 6-7NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72T 標(biāo)準(zhǔn)包裝:15 系列:74F 功能:異步 存儲(chǔ)容量:256(64 x 4) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:- 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:24-DIP(0.300",7.62mm) 供應(yīng)商設(shè)備封裝:24-PDIP 包裝:管件 其它名稱:74F433 |

| IDT72V01L15J | 功能描述:IC ASYNCH 512X9 15NS 32-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V01L15J8 | 功能描述:IC ASYNCH 512X9 15NS 32-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V01L15JG | 功能描述:IC ASYNCH 512X9 15NS 32-PLCC RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V01L15JG8 | 功能描述:IC ASYNCH 512X9 15NS 32-PLCC RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。